Task description and Expected results

This Task will be devoted entirely to the study and design of analog hardware components for the cognitive radio transceiver approach.

In this sense the TSK will be divided into two sub-tasks being each one devoted to different parts of the transceiver design, focusing on data communication and spectrum sensing receiver front end and data communications transmitter front end. Each of these blocks imposes different strategies to the analog design putting more emphasis on dynamic range, bandwidth and energy efficiency. STSK2.1 – Receiver Analog Front End

In the receiver analog front end, the new steps in the state of the art imposes different design strategies, based on the proposal of high dynamic range and wide bandwidth schemes. This is especially true due to the fact that a real cognitive radio will be multi-carrier and multi-standard and should receive the interesting signals in perfect conditions, i.e., it should resist to high power interference signals when receiving low power ones and should be capable to operate with multi-carrier modulated signals being simultaneously received. These statements impose high dynamic range needs mainly for the data communications front end but also for the sensing platform. The approach to follow on this project will be supported in previous experience from the team on the increase of the available dynamic range, which will be based on novel receiving architectures operating in a bandpass sampling schemes with parallel attenuated paths and also on post-compensation schemes that could be implemented in TSK8, or with analog strategies used to limit the nonlinear behaviour of the now proposed schemes.

Regarding the bandwidth limitations, the strategy to be followed here will be based on second-order bandpass sampling receivers, using wideband passive 90⁰ hybrids as the phase delay mechanism to imitate the ideal Hilbert transformation for image signal rejection. This design will require a strong collaboration with TSK8 to compensate the non-ideal behaviour of the entire receiver architecture. Moreover, advanced concepts in signal processing will be implemented with real hardware in order to understand the main drawbacks of these initial mathematical approaches.

STSK2.2 – Transmitter Analog Front End.

In the transmitter side, the analog design is focused mainly on the linearity and adaptability aspects versus high energy efficiency transmitters. This implies that some alternative techniques should be discussed and proposed to increase the power efficiency and simultaneously to allow adaptable approaches. Some of the strategies in this project is to combine digital and analog design including multi-level sigma-delta and pulse-width modulators, but also to explore new approaches.

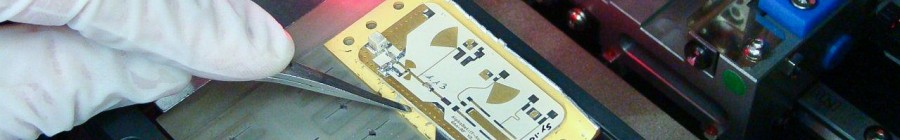

This sub-task will be devoted to the design of the analog part that will cope with these digital strategies by implementing bandwidth-optimized switching-mode PA’s. One of the possibilities to be considered will be on the design of class J PA. A strong analysis on the linearity enhancements and energy efficient will also be studied in order to guarantee that commercial masks are fulfilled. A strong connection exists between this STSK and the TSK on all digital transmitters (TSK5). In this task it is expected that a strong collaboration exists between the other TSK, and some strategies will change depending on the findings on other TSK’s.

At the end of this TSK it is expected that the state of the art will be improved in the following topics:

• Dynamic Range Increase

• Dynamic Range Increase

• Use of distortion cancellation designs

• Novel receiving architectures

• Selective clipping of interferers

• All digital Transmitters

• Increase the overall efficiency

• Combination of signal processing for highly efficient PA’s

The task will be based mainly on the expertise of IT-Aveiro and INESC -Porto team, since the large background in the area will allow a faster evolution time. In this task 4 PhD researchers, 3 PhD students and Bolseiros.

Members of the research team in this task: (BI) Bolseiro de Investigação (Mestre) 1; (BI) Bolseiro de Investigação (Mestre) 6; João Nuno Pimentel da Silva Matos; José Alberto Peixoto Machado da Silva; Nuno Miguel Gonçalves Borges de Carvalho; Pedro Miguel Duarte Cruz;