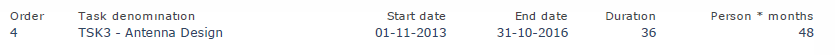

Task description and Expected results

This task will be entirely devoted to the study and design of reconfigurable digital hardware components for the cognitive radio

all-digital RF transmitter. In this sense the task will be divided into several sub-tasks focusing on:

- agile high performance all-digital transmitter architectures with advanced signal shaping techniques for superior multichannel

operation as well as for improved bandwidth and noise reduction.

- complete FPGA integration of the flexible transmitter supported by fast reconfiguration approaches.

Sub-task 5.1 – Power Efficient All-Digital Transmitters for C ognitive Radio

In the digital transmitter side, the main focus will be on designing high performance and agile FPGA-based All-Digital Transmitter

architectures suitable for C R-based applications (e.g. exploration of TV white spaces). This requires analyzing the tradeoffs

between important figures of merit, such as SNR, usable bandwidth, linearity and stability in order to propose new techniques

that enable to simultaneously achieve high adaptability, multichannel transmission and power efficiency. Some of the strategies

proposed by the team include the combined use of PWM with multi-level Delta-Sigma Modulation, novel noise cancellation

techniques and efficient exploration of the FPGA reconfigurable hardware resources, but also to study and explore new

approaches for implementing a new transmitter architecture where the tight coupling design of both digital and analog

components will favor the overall performance of the transmitter.

Sub-task 5.2 – FPGA Integration of the All-Digital Reconfigurable Transmitter for NC -OFDM-based C R Systems

This sub-task aims the integration of the results obtained in the previous sub-task with task 4 (Reconfigurable NC -OFDM

Processor for Multimode Spectrum Aggregation) and task 8 (Signal Processing for Hardware Optimization), in order to build a

fully FPGA integrated all-digital NC -OFDM reconfigurable transmitter with embedded digital compensation for improving the

linearity of the radio transmitter.

This sub-task will also address the efficient exploration of the high logic capacity and the heterogeneous resources of modern

FPGAs, as well as the integration of multiple transmitter blocks in the same C R node in order to improve important figures of

merit as flexibility, computational requirements, reconfiguration time, usable bandwidths, linearity, PAPR levels and power

efficiency. In fact, since the NC -OFDM system will use multiple noncontiguous narrower sub-bands, this approach will allow

exploring the partitioning of the transmitter into multiple cells as a way to improve the above mentioned figures of merit.

The work to be performed in this sub-task will benefit from the knowledge of the research team in the topics of FPGA-based upconversion

of GHz range signals, advanced signal shaping algorithms and partial dynamic reconfiguration methodologies.

At the end of this task it is expected that the state of the art will be advanced in the following points:

- Advanced digital signal shaping techniques and corresponding implementation circuits that allow a fully FPGA-based flexible

processing of high bandwidth signals.

- New noise cancellation models and its efficient implementation in reconfigurable hardware for enabling the RF signal

transmission with improved power efficiency and lower filtering requirements but without sacrificing the adaptability.

- Novel baseband to RF up-conversion techniques and corresponding fully integrated FPGA-based realization circuits that allow

using flexible hardware modules for configurable and simultaneous multichannel and multi-standard operation.

- Tight integration of signal shaping and up-conversion techniques with FPGA-based baseband processing engines for high

throughput, low latency and fast reconfiguration times.

Mem bers of the research team in this task: (BI) Bolseiro de Investigação (Mestre) 2; (BI) Bolseiro de Investigação (Mestre) 5; Arnaldo Silva Rodrigues de Oliveira; João

Paulo C astro C anas Ferreira; José Alberto Peixoto Machado da Silva; Manuel José Alves Ventura da Silva; Nelson José Valente

da Silva; Nuno Miguel Gonçalves Borges de C arvalho; WONHOON JANG;