# Prediction of IMD in LDMOS Transistor Amplifiers Using a New Large-Signal Model

Christian Fager, *Student Member, IEEE*, José Carlos Pedro, *Senior Member, IEEE*, Nuno Borges de Carvalho, *Member, IEEE*, and Herbert Zirath, *Member, IEEE*

Abstract—In this paper, the intermodulation distortion (IMD) behavior of LDMOS transistors is treated. First, an analysis is performed to explain measured IMD characteristics in different classes of operation. It is shown that the turn-on region plays an important role in explaining measured IMD behavior, which may also give a clue to the excellent linearity of LDMOS transistors. Thereafter, with this knowledge, a new empirical large-signal model with improved capability of predicting IMD in LDMOS amplifiers is presented. The model is verified against various measurements at low as well as high frequency in a class-AB power amplifier circuit.

*Index Terms*—Intermodulation distortion, large signal, LDMOS, model, power amplifiers.

### I. INTRODUCTION

N MOST MODERN wireless systems, the linearity requirements put strong restrictions on the power amplifiers used. It has been found that LDMOS transistors exhibit better intermodulation distortion (IMD) performance compared to competing technologies [1], [2]. LDMOS transistors are, therefore, widely used in power amplifiers at microwave frequencies in commercial applications such as base–station transmitters.

IMD behavior in MESFET amplifiers has been treated in [3]. The analysis combines Volterra series for low input power with describing functions and harmonic balance for higher input power. It is shown that transitions between these input power regimes can explain measured IMD behavior such as sweetspots in MESFETs.

Using a similar approach, we show in this paper that the sharp turn-on region, compared to MESFETs, makes it necessary to revise the analysis in [3] for LDMOS transistors. The appearance of double third-order IMD (IM3) minima in class AB that has been observed by other authors [1], [4] can then be explained.

The double IMD sweet-spots close to the compression point in class AB present a great potential advantage since similar linearity performance as for class A then can be achieved at a substantially improved efficiency.

Manuscript received April 5, 2002; revised August 26, 2002. This work was supported by the Swedish Foundation for Strategic Research (SSF), Chalmers Centre for High Speed Technology (CHACH), Vinnova, and the Portugese Science Bureau (FCT) under the project LDMOSCA.

C. Fager and H. Zirath are with the Microwave Electronics Laboratory, Chalmers University of Technology, 412 96 Gothenburg, Sweden (e-mail: fager@ep.chalmers.se).

J. C. Pedro and N. B. de Carvalho are with the Instituto de Telecomunicações, University of Aveiro, 3810-193 Aveiro, Portugal.

Digital Object Identifier 10.1109/TMTT.2002.805187

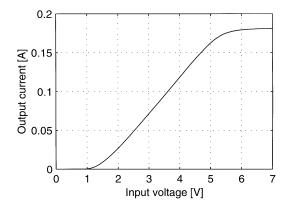

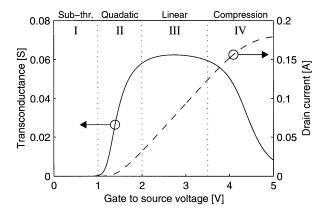

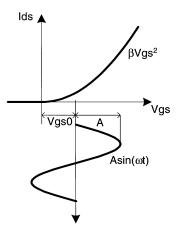

Fig. 1. Typical LDMOS transfer function  $I_{\text{out}}(V_{\text{in}})$ .

Commonly used LDMOS large-signal models [5]–[8], including the industry-standard MET-model, do not treat the turn-on region carefully enough and thus cannot predict measured IMD accurately.

A new empirical LDMOS large-signal model is therefore formulated in which the turn-on region of the transistor characteristic is treated independently from other modeling regions. As a result simulated IMD as well as output power and efficiency agree well with measurements. The model is formulated in a way similar to the MET model and is, therefore, easy to adopt.

## II. IMD ANALYSIS

The IMD is analyzed by studying the input voltage/output current transfer function (TF),  $I_{\rm out}(V_{\rm in})$ . The TF is found from the transistor  $I_{ds}(V_{gs},V_{ds})$  characteristics in combination with the drain bias, load impedance, and transistor parasitic elements. For MESFETs this has been done in [3]. Fig. 1 shows a typical TF obtained at low frequency for an LDMOS transistor in an amplifier application.

Since the transistor is usually biased with low quiescent current in the saturated region, the TF is essentially the  $I_{ds}(V_{gs})$  characteristic for low output currents. At higher currents, it is saturated by either the load-line entering the triode region, or compression due to the JFET-effect in the LDMOS drift region [9].

To study the LDMOS IMD behavior, a two-tone test is often used. The input voltage will then have the form

$$v_{\rm in}(t) = A\left(\sin\left(\omega_1 t\right) + \sin\left(\omega_2 t\right)\right). \tag{1}$$

At low excitation power, a Volterra series analysis may then be used to calculate the IM3 in  $I_{\text{out}}(v_{\text{in}})$ . IM3 is here used as a

0018-9480/02\$17.00 © 2002 IEEE

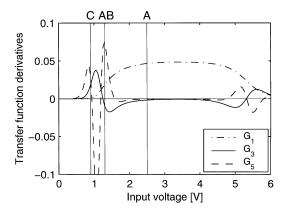

Fig. 2. Typical LDMOS transfer function derivatives versus input voltage  $V_{\rm in}$ . The bias voltages for different classes of operation are indicated on top of the figure.

general notation for the IMD sidebands appearing closest to the carriers, even if they usually are composed of also higher order IMD components.

The small-signal upper sideband IM3 at  $2\omega_2 - \omega_1$  in  $I_{\text{out}}$  is given by [10]

$$I_{\text{out,SS}}(\omega_{1}, \omega_{2})$$

$$= 2 \cdot \text{Re} \left[ \frac{3A^{3}}{8} H_{3}(\omega_{2}, \omega_{2}, -\omega_{1}) e^{j(2\omega_{2} - \omega_{1})t} + \frac{50A^{5}}{32} H_{5}(\omega_{2}, \omega_{2}, -\omega_{1}, \omega, -\omega) e^{j(2\omega_{2} - \omega_{1})t} \right]$$

$$= 2 \cdot \text{Re} \left[ I_{\text{out,SS}}^{[-1,2]}(\omega_{1}, \omega_{2}) e^{j(2\omega_{2} - \omega_{1})} \right]$$

(2)

where the superscript [-1,2] indicates the frequency component considered.  $H_3(\cdot)$  and  $H_5(\cdot)$  are nonlinear transfer functions and  $\varphi_1$  and  $\varphi_2$  phase constants. At low frequency, the Volterra series analysis turns into a power series analysis of the TF around the quiescent voltage [10]. The TF is then described by

$$I_{\text{out}}(v_{\text{in}}) = I_{\text{out,DC}} + G_1 v_{\text{in}} + G_2 v_{\text{in}}^2 + G_3 v_{\text{in}}^3 + G_4 v_{\text{in}}^4 + G_5 v_{\text{in}}^5$$

(3)

where the coefficients  $G_n$  represent the TF derivatives.

Fig. 2 shows typical LDMOS TF derivatives obtained using a large-signal model (see Section IV). The coefficients  $G_n$  are related to the nonlinear transfer functions so that the IM3 content in  $I_{\rm out}$  can be expressed as [3]

$$I_{\text{out,SS}}^{[-1,2]} = \frac{3A^3}{4}G_3 + \frac{25A^5}{8}G_5.$$

(4)

At low input power, IM3 is dominated by the third-order  $G_3$  term, which results in a 3-dB/dB slope of IM3 versus input power. Equation (4) also shows that an interaction between third- and fifth-order derivatives of opposite signs can give rise to a large-signal IMD sweet-spot [3]. However, since the contribution from the  $G_5$  term is usually much smaller, this happens at an input power level beyond the validity of the low-order Volterra series analysis used.

As the input power is increased, the signal excursion eventually reaches a region where the low-order power series in (3) no

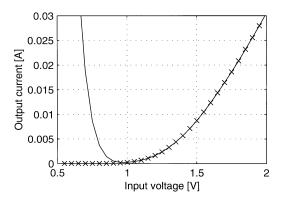

Fig. 3. Detailed view of the turn-on region, showing  $I_{\rm out}(\times)$  and a tenth-order Taylor series expansion (line) around  $V_{\rm in}=1.5\,$  V.

longer describes the TF adequately. These regions usually correspond to strong nonlinearities such as breakdown, gate forward conduction, or saturation due to the load line entering the triode region. In [3], a two sinusoidal input describing function (TSIDF) has been used to analyze the IMD for this purpose. The TSIDF for the IM3 product at  $2\omega_2-\omega_1$  is, in this case, defined as

$$I_{\text{out,LS}}^{[-1,2]}(\omega_{1},\omega_{2}) = \frac{2j}{AT_{1}T_{2}} \int_{-T_{1}/2}^{T_{1}/2} \int_{-T_{2}/2}^{T_{2}/2} I_{\text{out}}(v_{\text{in}}(t_{1},t_{2})) e^{j\omega_{1}t_{1}} e^{-j2\omega_{2}t_{2}} dt_{1} dt_{2}$$

(5)

where  $v_{\rm in}(t_1,t_2)=A(\sin(\omega_1t_1)+\sin(\omega_2t_2))$ . It can be shown that  $I_{\rm out,LS}^{[-1,2]}(\omega_1,\omega_2)$  becomes negative as the input signal amplitude approaches infinity—or simply as the output signal compresses. Therefore, depending on the sign of IM3 found from the small-signal analysis in (4), different IM3 versus input power patterns can be predicted. Such results are presented for MESFET's in [3].

For LDMOS transistors, the high-order derivatives in the turn-on region are much larger than the ones presented for MESFETs (see Fig. 2). This indicates that high-order terms are necessary for describing the transition appropriately. Fig. 3 shows how even a tenth-order Taylor series expansion fails to describe the TF beyond the turn-on knee.

For LDMOS transistors, the IMD behavior must therefore be analyzed with large-signal TSIDF techniques not only when the saturation region is reached, but also as soon as the input signal traverses the turn-on knee.

It is shown in the Appendix that the turn-on knee gives a positive IM3 contribution and therefore is an expanding nonlinearity as soon as the input signal traverses the knee. The amount of positive contribution is determined by the knee abruptness and the input amplitude.

Different distinct IMD characteristics can now be depicted from transitions between the contributions in the small-signal, turn-on, and large-signal regions. For example, the expanding and compressing nonlinearities of the turn-on and saturation regions, respectively, can counteract each other to create an overall more linear operation. The same principle is in fact used in predistortion linearization of power amplifiers [11].

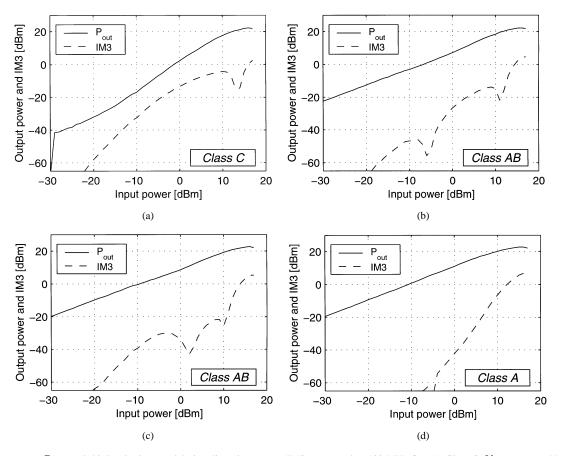

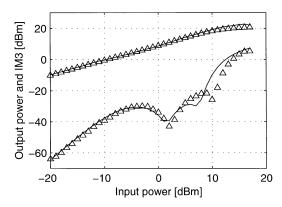

Fig. 4. Output power ( $P_{\rm out}$ ) and third-order intermodulation distortion power (IM3) measured at 100 MHz for: (a) Class C,  $V_{gs,\rm dc}=0.9$  V; (b) Class AB,  $V_{gs,\rm dc}=1.2$  V; (c) Class AB,  $V_{gs,\rm dc}=1.3$  V; and (d) Class A,  $V_{gs,\rm dc}=2.5$  V.

## III. MEASURED IMD BEHAVIOR

Two-tone measurements, shown in Fig. 4, have been performed to study LDMOS IMD behavior. The transistor used has  $I_{dss}=175~\mathrm{mA}$  and was biased at  $V_{ds,\mathrm{dc}}=20~\mathrm{V}$  [12]. The measurements were made in a 50  $\Omega$  environment at 100 MHz with 1-MHz frequency separation.

Depending on the class of operation, the different distinct IMD characteristics can now be explained using the behavioral analysis in the previous section.

## A. Class-C Operation

From Fig. 2, the third-order derivative of the transfer function is seen to be positive in class C,  $V_{\rm in,dc}=0.9$  V. Thus, from (4) this implies that IM3 is also positive for low input power levels. The additional positive contribution from the turn-on region results in a further increase in the slope of the IMD curve and gain expansion. However, when the output power saturates, IM3 must become negative. Hence, an IMD minimum occurs near the compression point. Fig. 4(a) shows the measured output power and IM3 for this case. Similar IMD behavior has been observed in class-C MESFET amplifiers [1], [3], [13].

This kind of sweet-spot near the output power compression point, gives locally a very large carrier-to-intermodulation (C/I) ratio. However, in real amplifiers the input power may vary. It is therefore difficult to make use of this phenomenon for sufficient IMD suppression in those applications.

# B. Class-AB Operation

To achieve better IMD performance while maintaining acceptable gain and efficiency, amplifiers are commonly designed to operate in class AB. This corresponds to a negative  $G_3$  as seen in Fig. 2. The measured output power and IM3 for two bias voltages  $V_{\rm in,dc}=1.2$  V and  $V_{\rm in,dc}=1.3$  V in class AB are shown in Fig. 4(b) and (c), respectively.

The first of the two minima appears when the negative contribution from  $G_3$  is cancelled by the positive IM3 contribution from the turn-on region. Since the turn-on region influence is much stronger, the minimum appears as soon as the input signal reaches that region. The minimum will therefore occur at higher input power if the transistor is biased further away from turn-on. This is confirmed by comparing the IM3 measurements. As the input power is further increased, IM3 will remain positive until the output power compresses and IM3 must again become negative. This change of sign creates another sweet-spot, close to the compression point.

By a proper choice of gate bias, the two minima can be combined to create a large C/I ratio over a much wider input power range near the compression point compared to class-C operation [(see Fig. 4(c)].

Note that this behavior is only possible because of the expanding nonlinearity of the sharp turn-on knee in LDMOS transistors. The same behavior is generally not observed in MESFETs.

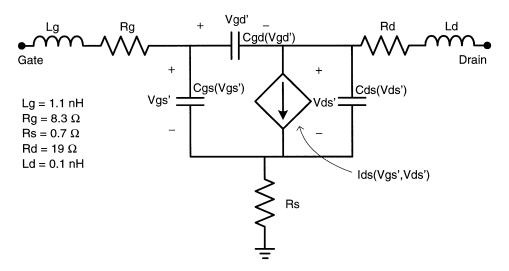

Fig. 5. Simple LDMOS large-signal model topology used.

## C. Class-A Operation

As the bias is increased toward class A,  $G_3$  will remain negative. The difference compared to class AB is that the input signal will now reach the output power saturation region before the turn-on region. IM3 will, therefore, remain negative and thus no IMD minimum is observed in Fig. 4(d).

Class A is usually considered the most linear mode of operation. Fig. 4 shows, however, that class AB may in fact be more linear over a wide input power range due to the double minima present.

The results in this and the previous section present a great potential advantage for LDMOS transistors, due to the existence of two IMD minima in class AB. Thereby, similar IMD performance as in class A can be achieved with a significantly improved efficiency.

The turn-on region, which is found very important for IMD when biased in class AB, is not accurately described in commonly used LDMOS large-signal models. In the following section, a new large-signal model is, therefore, presented where special care is taken to properly model the turn-on region. Thereby, IMD as well as output power and efficiency may be predicted very well.

## IV. LARGE-SIGNAL MODEL

In this section, a new empirical large-signal model is proposed. A simple model topology, shown in Fig. 5, has been used, where the parasitic and intrinsic small-signal parameter values have been found for various bias voltages using a robust multibias extraction technique [14].

First, modeling of the nonlinear current source  $I_{ds}(V_{qs}, V_{ds})$ is treated.

# A. Nonlinear Drain Current Model

Fig. 6 shows measured  $I_{ds}$  and extracted small-signal transconductance  $(g_m)$  plotted versus  $V_{qs}$  when the LDMOS is biased in the saturated region. The transconductance characteristics can be divided in different regions, each having its dominant physical origin. As discussed in previous sections,

Fig. 6. Typical LDMOS transconductance  $g_m$  and drain current  $I_{ds}$  with different operating regions indicated.

accurate description of the knee-region is very important for prediction of IMD in LDMOS transistors.

In region I, the subthreshold region, the drain current is usually taken to depend exponentially on the gate voltage [15]. When the voltage is further increased, the current starts to rise quadratically (region II), which implies that  $g_m$  should rise linearly. The quadratic behavior is observed in MOS and LDMOS transistors [15]–[17].

The current in and between the subthreshold and quadratic regions is often modeled with [16], [17]

$$V_{gs1} = V_{gs} - V_t \tag{6}$$

$$V_{gst} = VST \ln \left( 1 + e^{V_{gs1}/VST} \right) \tag{7}$$

$$V_{gs1} = V_{gs} - V_t$$

$$V_{gst} = VST \ln \left( 1 + e^{V_{gs1}/VST} \right)$$

$$I_{dsq} = \beta V_{gst}^2$$

(8)

where VST controls the turn-on abruptness,  $V_t$  the turn-on voltage, and  $\beta$  the slope in the quadratic region.

For higher voltages (region III), short channel effects such as velocity saturation make  $I_{ds}$  approach a linear dependence on  $V_{qs}$  with a resulting constant transconductance.

Devices are usually designed to present constant transconductance over a region as wide as possible to achieve better IMD performance. This gives good linearity in class A operation but, as shown in previous sections, it is no guarantee for better IMD performance in high efficiency linear amplifier applications.

Many large-signal LDMOS models, including the industry-standard MET model, do not address the quadratic region, but make the transition directly from the exponential subthreshold region to the linear region [4], [6], [8]. Thus, no parameters are available to define the turn-on knee abruptness and the knee tends to be too smooth. As described in Section II, this may severely affect its ability of predicting IMD behavior properly.

We have chosen to implement the transition from quadratic to linear regions using the following empirical expression:

$$I_{ds} = \frac{\beta V_{gst}^2}{1 + \frac{V_{gst}^{plin}}{V_I}} \tag{9}$$

where the parameter VL in combination with  $\beta$  controls the slope of the quadratic region and transition to the linear region. The parameter p lin is added to tune the transconductance slope in the linear region. In most cases, p lin = 1.

For higher  $V_{gs}$ , the transconductance will drop and the current compresses (region IV). This is typical for LDMOS transistors and is caused by the low-doped drift region acting as a grounded gate JFET in series with the intrinsic MOSFET transistor. For high currents, the JFET will force the intrinsic MOSFET to operate toward lower drain voltages where the transconductance is substantially lower [9]. A successful way of modeling this, which is used in the MET model, is to introduce an effective  $V_{gs}$  that saturates at a constant voltage, VK. The effective  $V_{gs}$  is given by [5]

$$V_{gs2} = V_{gs1} - \frac{1}{2} \left( V_{gs1} + \sqrt{(V_{gs1} - VK)^2 + \Delta^2} - \sqrt{VK^2 + \Delta^2} \right). \quad (10)$$

The proposed set of equations defining the nonlinear current source is given as follows:

$$V_{gs1} = V_{gs} - V_t$$

$$V_{gs2} = V_{gs1} - \frac{1}{2} \left( V_{gs1} + \sqrt{(V_{gs1} - V_K)^2 + \Delta^2} \right)$$

(11)

$$-\sqrt{VK^2 + \Delta^2}$$

(12)

$$V_{gs3} = VST \ln \left( 1 + e^{V_{gs2}/VST} \right) \tag{13}$$

$$I_{ds} = \frac{\beta \cdot V_{gs3}^2}{1 + \frac{V_{gs3}^{plin}}{V_{ds}}} \cdot (1 + \lambda V_{ds}) \tanh\left(\frac{\alpha \cdot V_{ds}}{V_{gs3}^{psat}}\right)$$

(14)

where the drain voltage dependence is taken from the MET model [5], [7].  $\lambda$  and  $\alpha$  are standard model parameters [5], [7], [16]. The parameter psat controls the transition from triode to saturated region.

A simple thermal *R*–*C* circuit was also added to take care of self-heating effects [4].

Some of the parameters used may be nonconstant, depending on the accuracy required, e.g.,

$$V_t = V_{t0} + \gamma V_{ds} \tag{15}$$

$$\beta = \beta_0 + \beta_1 \left( T - T_{\text{nom}} \right) \tag{16}$$

$$\alpha = \alpha_0 + \alpha_k V_{ast} \tag{17}$$

$$VK = VK_0 + \gamma_{sat} V_{ds}. \tag{18}$$

Various possible dependencies of the model parameters—such as temperature, bias, and scaling effects—are beyond the scope of this paper, but have been investigated in [6] and [16].

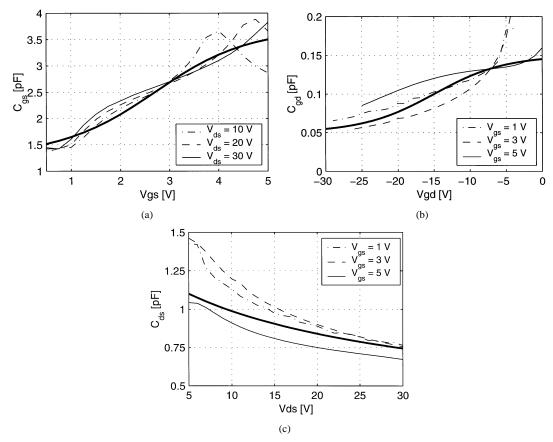

#### B. Nonlinear Capacitances

At normal operating frequencies, the influence of nonlinear capacitances also has to be considered [7], [18]. The voltage dependence of the capacitances may be studied from the small-signal parameter extraction. Fig. 7 shows the extracted capacitances and the simple nonlinear models used.

For  $C_{gs}$  and  $C_{gd}$ , simple empirical hyperbolic tangent expressions have been used

$$C_{gx}(V_{gx}) = C_{gx0} + \frac{A_{Cgx}}{2} \left( 1 + \tanh\left[k_{Cgx} \left(V_{gx} - V_{Cgx}\right)\right] \right)$$

(19)

where  $C_{gx0}$  is the offset value and  $A_{Cgx}$  affects the magnitude of the capacitance nonlinearity.  $V_{Cgx}$ , and  $k_{Cgx}$  control the center and abruptness of the capacitance nonlinearity, respectively. A simple depletion capacitance model is used for  $C_{ds}[15]$

$$C_{ds}(V_{ds}) = \frac{C_{ds0}}{\sqrt{1 + \frac{V_{ds}}{V_{ds0}}}}$$

(20)

with  $C_{ds0}$  and  $V_{ds0}$  being the model parameters.

# C. Model Verification

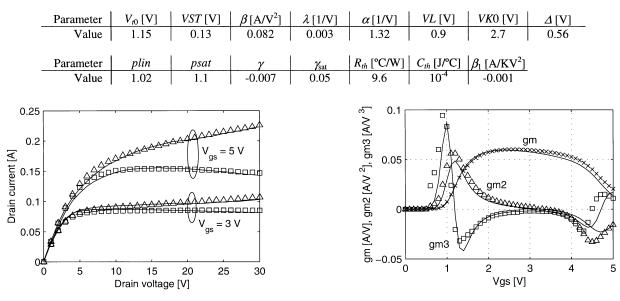

The current-source model parameters were found using a manual fitting procedure where extracted small-signal transconductance and measured pulsed and static drain current characteristics were used. Table I shows the total set of model parameters obtained.

Fig. 8 shows measured and modeled I/V characteristics for pulsed and static conditions.

It is well known that a model should predict not only  $I_{ds}$  but also its higher order derivatives to predict IMD accurately [19], [20]. Fig. 9 shows measured and modeled derivatives. Since static nonisothermal measurements were used, thermal effects make extraction of  $g_m$  and its derivatives more uncertain at high  $V_{qs}$ .

The derivatives have been extracted at 10 MHz and  $V_{ds}=20~{\rm V}$  using a setup presented in [19]. In the setup, sinusoidal signals of low amplitude and slightly different frequency are applied simultaneously to the gate and drain terminals. By studying the resulting intermodulation products in the drain current using a spectrum analyzer, and knowing the small-signal equivalent circuit, makes it possible to determine the nonlinear current source derivatives. The resulting measurement accuracy is very good as indicated by the regularity of the measured derivatives.

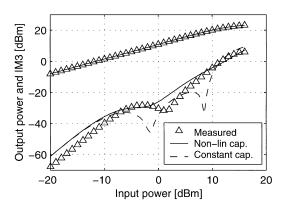

The accuracy of the nonlinear current part of the model is demonstrated by its ability to predict the IMD measurements shown in the previous section. Fig. 10 shows measured and modeled IM3 at  $V_{gs}=1.3~\rm{V}$ .

Similar measurements showing double IMD sweet-spots have been presented in [4], where it was simply concluded

Fig. 7. Extracted small-signal capacitances (thin lines) and the corresponding nonlinear capacitance models (thick lines).

TABLE I CURRENT-SOURCE MODEL PARAMETERS.

Fig. 8. Measured (markers) and modeled (lines) drain current for static ( $\square$ ) and pulsed ( $\triangle$ ) conditions.

that "the [IMD] data has unusual structure." The MET model used in that case did not predict the existence of double IMD sweet-spots.

At high frequency, large influence of nonlinear capacitances on intermodulation generation has been reported for MESFET's and LDMOSFET's [7], [18]. This is confirmed in Fig. 11 where

Fig. 9. Measured and simulated  $I_{ds}$  derivatives versus  $V_{gs}$  at  $V_{ds}=20~{\rm V}.$

a false IMD minimum is simulated near the compression point when constant capacitances, taken as the small-signal values at the bias point, are used.

Compared to the measurements at low frequency, the non-linear capacitances tend to smoothen the IMD behavior making only one less pronounced sweet-spot appear. Thus, the IMD improvements compared to class A are reduced. However, proper

Fig. 10. Measured (markers) and simulated (lines) output power and IM3 at  $V_{qs}=1.3~{\rm V}, V_{ds}=20~{\rm V},$  and  $f=100~{\rm MHz}.$

Fig. 11. Comparison between measured and simulated output power and IM3 for the cases of nonlinear and constant capacitances. The comparison is made at  $f=1.9~\mathrm{GHz}, V_{gs}=1.2~\mathrm{V},$  and  $V_{ds}=28~\mathrm{V}.$  Terminating impedances were adjusted for maximum output power.

tuning of the harmonic terminating impedances might restore the performance.

A slight shift toward lower power level is seen in the simulation for the sweet-spot.

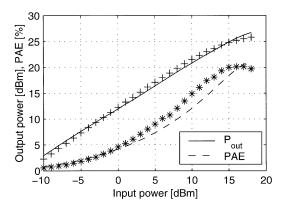

### V. POWER AMPLIFIER CIRCUIT EXAMPLE

A 1900-MHz power amplifier for 28-V supply voltage was built using the same device as in previous sections to examine the IMD behavior at high frequency in a real circuit environment. The amplifier was designed to operate in class AB with the input matched for maximum gain and the output impedance chosen for maximum output power [21]. The output network was designed to short-circuit signals at second harmonic and baseband to improve the IMD behavior [3].

Measured and simulated output power and efficiency are shown versus input power in Fig. 12. The simulations were made using the model presented in Section IV.

The maximum power added efficiency (PAE) is quite low, 20%. It can be explained by the large drain resistance  $R_d=19\,\Omega$  in the extracted model.  $R_d$  is set by losses in the substrate and the low-doped drift region. However, simulations indicate that the efficiency rises drastically at lower frequency as the reactive currents through  $R_d$  are reduced.

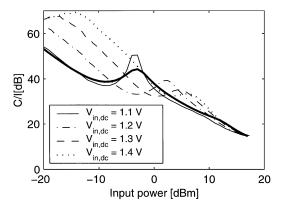

The IMD performance was studied using a two-tone test with 1-MHz frequency separation. Fig. 13 shows measured C/I

Fig. 12. Measured (markers) and simulated output power and PAE.

Fig. 13. Measured C/I versus input power at different input bias voltages. The thick line corresponds to a simulation made at  $V_{\rm in,dc}=1.2$  V.

for various input bias voltages. A simulation is also shown for  $V_{

m in,dc}=1.2~{

m V}.$

The results in Fig. 13 agree well with the simulation except for a 0.1-V bias voltage offset. As discussed in Section IV, only one IMD sweet-spot is present at high frequency due to the nonlinear capacitances.

Nevertheless, as predicted in the low frequency analysis for operation in class AB, the measurements validate however that a bias-dependent IMD sweet-spot is present also at higher frequencies.

# VI. CONCLUSIONS

First, the IMD behavior in LDMOS transistor amplifiers has been analyzed using a behavioral analysis. The analysis has shown that the sharp turn-on knee compared to, e.g., MESFETs plays an important role in understanding measured IMD behavior. The existence of two IMD sweet-spots in class AB operation could be predicted, and presents an important advantage for LDMOS transistors. Better efficiency may then be achieved with similar linearity as in class A.

Since most commonly used large-signal models do not address the turn-on region, specifically, a new large-signal model was also presented with special treatment of the turn-on knee for accurate prediction of the observed IMD sweet-spots. Nonlinear capacitances are also shown to play an important role for prediction of IMD at high frequency. The model predicts various lowand high-frequency measurements of dc, output power, IMD, and efficiency characteristics well.

Fig. 14. Idealized description of the transistor turn-on region and the applied input signal.

## APPENDIX

It will be shown that the turn-on region gives a positive IM3 contribution and, therefore, is an expanding nonlinearity as soon as the input signal traverses it.

The harmonic generation from a single sinusoidal input signal is used since the third harmonic content is a direct measure of the IM3 generation that will occur in a two-tone test.

To ease algebraic calculations, the turn-on region is idealized as shown in Fig. 14, where the current goes abruptly from zero to a quadratic  $V_{qs}$  dependence.

The sinusoidal input signal in Fig. 14 can be expressed as

$$V_{as}(t) = V_{as0}(1 + a\cos(\omega t)) \tag{A1}$$

where  $a = A/V_{gs0}$ .

If a < 1 the input signal does not reach the knee. Then, since a purely quadratic nonlinearity is considered,  $I_{ds}$  will not contain any odd-order harmonics other than the fundamental frequency and no IM3 can be generated. The fundamental frequency content of  $I_{ds}$  is in this case given by

$$I_{ds}^{[1]} = 2a\beta V_{as0}^2$$

(A2)

When a>1, the output waveform will be clipped. This occurs at  $\tau=\pm\arccos(-1/a)/\omega$ . The fundamental and third harmonic content in  $I_{ds}$  will then be given by

$$I_{ds}^{[1]} = \frac{2}{T} \int_{-\tau}^{\tau} \beta V_{gs}^{2}(t) \cos(\omega t) dt$$

(A3)

$$I_{ds}^{[3]} = \frac{2}{T} \int_{-\tau}^{\tau} \beta V_{gs}^{2}(t) \cos(3\omega t) dt \tag{A4}$$

where  $T = 2\pi/\omega$ , which yields

$$I_{ds}^{[1]} = 2a\beta V_{gs0}^2 \left[ 1 - \frac{1}{\pi} \arccos\left(\frac{1}{a}\right) + \frac{\sqrt{a^2 - 1}}{3\pi} \left(2 + \frac{1}{a^2}\right) \right]$$

$$\underset{a\gg 1}{\longrightarrow} 2a\beta V_{gs0}^2 \left(\frac{1}{2} + \frac{2a}{3\pi}\right) \tag{A5}$$

$$I_{ds}^{[3]} = \frac{4\left(a^2 - 1\right)^{5/2}\beta V_{gs0}^2}{15\pi a^3} \xrightarrow[a \gg 1]{} \frac{4a^2\beta V_{gs0}^2}{15\pi}.$$

(A6)

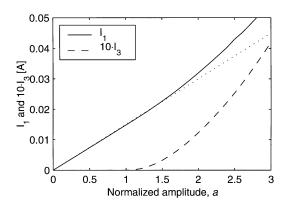

Fig. 15. Harmonic generation versus normalized input amplitude a. The dotted line indicates the extended linear  $I^{[1]}$ .

These equations show that the knee-region represents in fact an expanding nonlinearity with a positive IM3 contribution as soon as the input signal traverses the turn-on knee.

Fig. 15 presents the fundamental and third harmonic content in  $I_{ds}$  versus normalized input drive level, a. The parameters are chosen to match the device used. Comparison with a more accurate model for the turn-on knee shows small difference.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. K.-H. Eklund and Dr. J. Olsson, Department of Solid State Electronics, Uppsala University, Uppsala, Sweden, and Dr. N. Rorsman and Dr. K. Yhland, Department of Microwave Electronics, Chalmers University, Göteborg, Sweden, for fruitful discussions and providing devices for the measurements.

### REFERENCES

- [1] S. R. Novis and L. Pelletier, "IMD parameters describe LDMOS device performance," *Microw. RF*, vol. 37, pp. 69–74, July 1998.

- [2] J.-J. Bouny, "Advantages of LDMOS in high power linear amplification," *Microw. Eng. Eur.*, pp. 37–40, Apr. 1996.

- [3] N. B. Carvalho and J. C. Pedro, "Large- and small-signal IMD behavior of microwave power amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. 47, pp. 2364–74, Dec. 1999.

- [4] W. R. Curtice et al., "A new dynamic electro-thermal nonlinear model for silicon RF LDMOS FET's," 1999 IEEE MTT-S Int. Microwave Symp. Dig., vol. 2, pp. 419–22, 1999.

- [5] Motorola's Electro Thermal (MET) LDMOS Model. [Online]. Available: http://e-www.motorola.com/collateral/LD-MOSMODELS-RF.html

- [6] Y. Yang, Y. Y. Woo, J. Yi, and B. Kim, "A new empirical large-signal model of Si LDMOSFET's for high-power amplifier design," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 1626–33, Sept. 2001.

- [7] M. Miller, T. Dinh, and E. Shumate, "A new empirical large signal model for silicon RF LDMOS FET's," 1997 IEEE MTT-S Symp. Technologies for Wireless Applications Dig., pp. 19–22, 1997.

- [8] L. Bengtsson, I. Angelov, H. Zirath, and J. Olsson, "An empirical high-frequency large-signal model for high-voltage LDMOS transistors," in Proc. 28th European Microwave Conf., vol. 1, 1998, pp. 733–8.

- [9] P. Perugupalli, M. Trivedi, K. Shenai, and S. K. Leong, "Modeling and characterization of an 80 V silicon LDMOSFET for emerging RFIC applications," *IEEE Trans. Electron Devices*, vol. 45, pp. 1468–78, July 1998.

- [10] S. A. Maas, Nonlinear Microwave Circuits. Norwood, MA: Artech House, 1988.

- [11] P. Kenington, High Linearity RF Amplifier Design. Norwood, MA: Artech House, 2000.

- [12] J. Olsson et al., "1 W/mm RF power density at 3.2 GHz for a dual-layer RESURF LDMOS transistor," *IEEE Electron Device Lett.*, vol. 23, pp. 206–8, Apr. 2002.

- [13] C. C. Blanco, "Gain expansion and intermodulation in a MESFET amplifier," *Electron. Lett.*, vol. 15, pp. 31–2, July 1979.

- [14] C. van Niekerk, P. Meyer, D. M. M.-P. Schreurs, and P. B. Winson, "A robust integrated multibias parameter-extraction method for MESFET and HEMT models," *IEEE Trans. Microwave Theory Tech.*, vol. 48, pp. 777–86, May 2000.

- [15] Y. Tsividis, Operation and Modeling of the MOS Transistor, 2 ed. Boston, MA: WCB/McGraw-Hill, 1999.

- [16] A. V. Grebennikov and F. Lin, "An efficient CAD-oriented large-signal MOSFET model," *IEEE Trans. Microwave Theory Tech.*, vol. 48, pp. 1732–42, Oct. 2000.

- [17] C. C. Enz, F. Krummenacher, and E. A. Vittoz, "An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications," *Analog Integrated Circuits Signal Process.*, vol. 8, pp. 83–114, 1995.

- [18] J. A. Garcia et al., "Characterizing the gate-to-source nonlinear capacitor role on GaAs FET IMD performance," *IEEE Trans. Microwave Theory Tech.*, vol. 46, pp. 2344–55, Dec. 1998.

- [19] J. C. Pedro and J. Perez, "Accurate simulation of GaAs MESFET's intermodulation distortion using a new drain-source current model," *IEEE Trans. Microwave Theory Tech.*, vol. 42, pp. 25–33, jan. 1994.

- [20] S. A. Maas and D. Neilson, "Modeling MESFET's for intermodulation analysis of mixers and amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. 38, pp. 1964–71, Dec. 1990.

- [21] S. C. Cripps, RF Power Amplifiers for Wireless Communications. Boston, MA: Artech House, 1999.

**Christian Fager** (S'98) was born in Varberg, Sweden, in 1974. He received the M.Sc. degree in electrical engineering in 1998 from Chalmers University of Technology, Gothenburg, Sweden, where he is currently working toward the Ph.D. degree in the Department of Microelectronics.

His research interests are in the areas of large-signal transistor modeling and nonlinear circuit design.

Mr. Fager received the Best Student Paper Award at the International Microwave Symposium in 2002.

José Carlos Pedro (S'90–M'95–SM'99) was born in Espinho, Portugal, in 1962. He received the diploma and doctoral degrees in electronics and telecommunications engineering, from the University of Aveiro, Aveiro, Portugal, in 1985 and 1993, respectively.

From 1985 to 1993, he was an Assistant Lecturer at the University of Aveiro, where, in 1993, he became an Assistant Professor. He is currently an Associate Professor and a Senior Research Scientist in the Telecommunications Institute at the university. His main scientific interests include active device mod-

eling and the analysis and design of various nonlinear microwave and optoelectronics circuits, in particular, the design of highly linear multicarrier power amplifiers and mixers. He has authored or coauthored several papers published in international journals and presented at symposia

Dr. Pedro received the Marconi Young Scientist Award in 1993 and the 2000 Institution of Electrical Engineers, U.K., Measurement Prize. He has served the IEEE as a Reviewer for the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES and the IEEE MTT-S International Microwave Symposium.

Nuno Borges de Carvalho (S'92–M'00) was born in Luanda, Portugal, in 1972. He received the diploma and doctoral degrees in electronics and telecommunications engineering from the University of Aveiro, Aveiro, Portugal, in 1995 and 2000, respectively.

From 1997 to 2000, he was an Assistant Lecturer at the University of Aveiro, where he currently is an Auxiliary Professor and a Senior Research Scientist in the Telecommunications Institute at the university. His main research interests include CAD and measurement of nonlinear circuits and design of RF-mi-

crowave power amplifiers. He has authored or coauthored several papers published in international journals and presented at symposia and he has been a Reviewer for several journals and symposia.

Dr. Carvalho is a member of the Portuguese Engineering Association. He was the recipient of the 1995 University of Aveiro and the Portuguese Engineering Association Prize for the best student at the University of Aveiro, the 1998 Student Paper Competition (third place) presented at the IEEE International Microwave Symposium and the 2000 Institution of Electrical Engineers, U.K., Measurement Prize. He is a member of the Editorial Board of the IEEE Transactions on Microwave Theory and Techniques.

Herbert Zirath (S'84–M'86) is currently the Head of the Microwave Electronics Laboratory in the Department of Microelectronics, Chalmers University of Technology, Gothenburg, Sweden, where he became a Professor in 1996. His main scientific area is high-frequency electronics, in particular, design and fabrication of InP-HEMT devices and circuits, SiC-MESFETs and diodes and GaN-HEMTs and related circuits, device modeling, including noise and large-signal models for FET and bipolar devices, and foundry-related MMICs for

microwave and millimeter-wave applications. He is also one of the founders of NORSE AB, a company specializing in SiC high-frequency components.