# ML605 PCIe x4 Gen2 Design Creation

**May 2010**

**XTP045**

#### **Overview**

- Virtex-6 PCle x4 Gen2 Capability

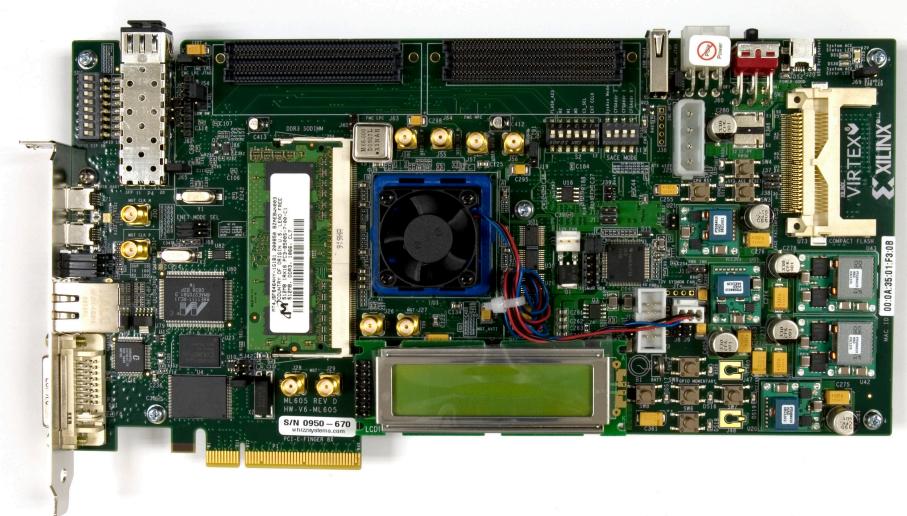

- Xilinx ML605 Board

- Software Requirements

- Generate PCle Core

- Compile PCle Core

- Program Platform Flash with PCle Design

- ML605 Setup

- Running the PCIe x4 Gen2 Design

- References

- IP Release Notes Guide XTP025

**Note:** This presentation applies to the ML605

## Virtex-6 PCIe x4 Gen2 Capability

- Integrated Block for PCI Express

- PCI Express Base 2.0 Specification

- Generation 2 (5 GT/s) data rates

- x4, x2, or x1 Gen2 lane width

- x8 Gen2 not supported in -1 parts

- Configurable for Endpoint or Root Port Applications

- ML605 configured for Endpoint Applications

- GTX Transceivers implement a fully compliant PHY

- Large range of maximum payload size

- 128 / 256 / 512 / 1024 bytes

- Configurable BAR spaces

- Up to 6 x 32 bit, 3 x 64 bit, or a combination

- Memory or IO

- BAR and ID filtering

- Management and Statistics Interface

# Xilinx ML605 Board

# **ISE Software Requirements**

Xilinx ISE 12.1 software

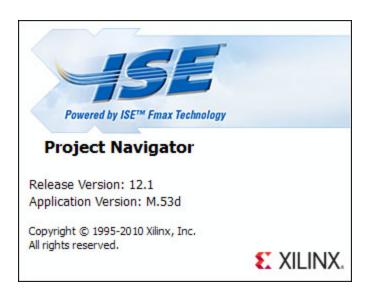

### **PciTree Software Requirement**

#### PciTree Bus Viewer

- Free download

- HLP.SYS must be copied to

C:\WINDOWS\system32\drivers

directory

Open the CORE Generator

Start  $\rightarrow$  All Programs  $\rightarrow$  Xilinx ISE Design Suite 12.1  $\rightarrow$  ISE  $\rightarrow$  Accessories  $\rightarrow$  CORE Generator

■ Create a new project; select File → New Project

Note: Pre-built design, RDF0009, available through http://www.xilinx.com/ml605

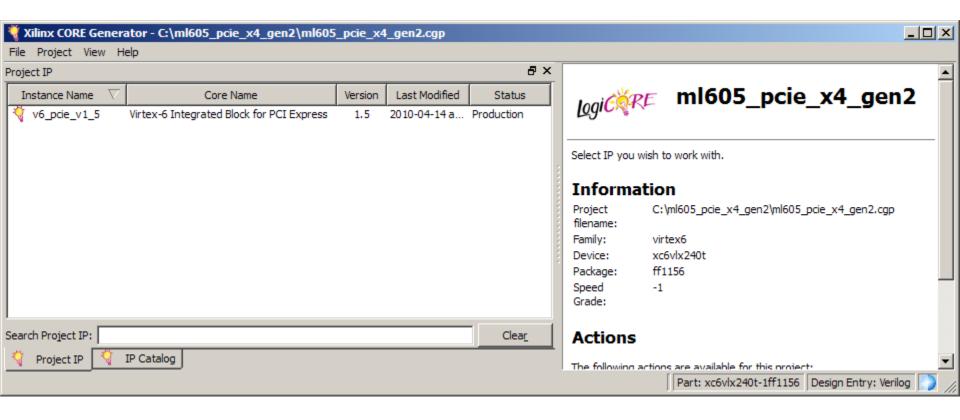

- Create a project directory: ml605\_pcie\_x4\_gen2

- Name the project: ml605\_pcie\_x4\_gen2.cgp

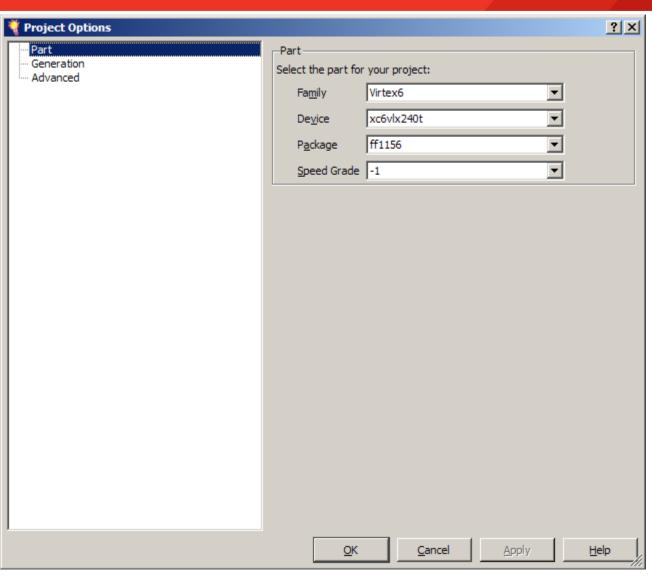

- The Project options will appear

- Set the Part (as seen here):

- Family: Virtex6

- Device: xc6vlx240t

- Package: ff1156

- Speed Grade: -1

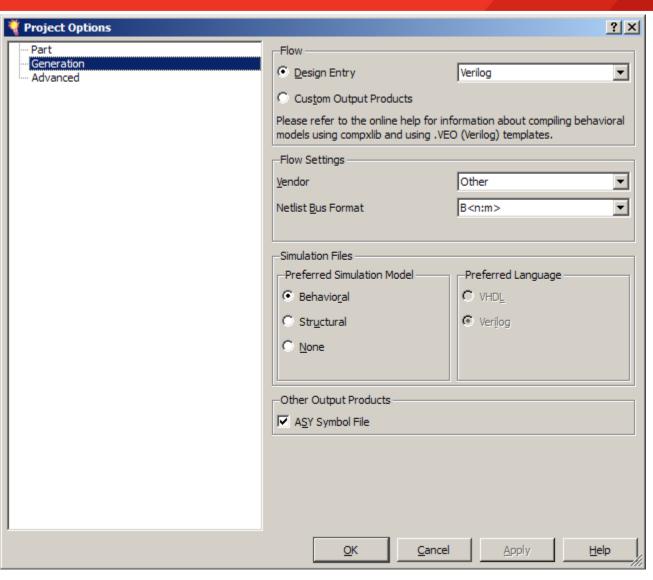

- Select Generation

- Set the Design Entry to Verilog

- Click OK

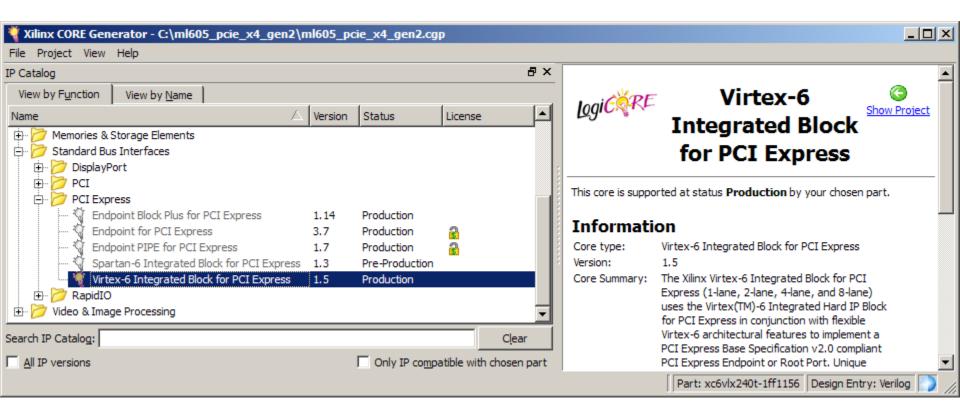

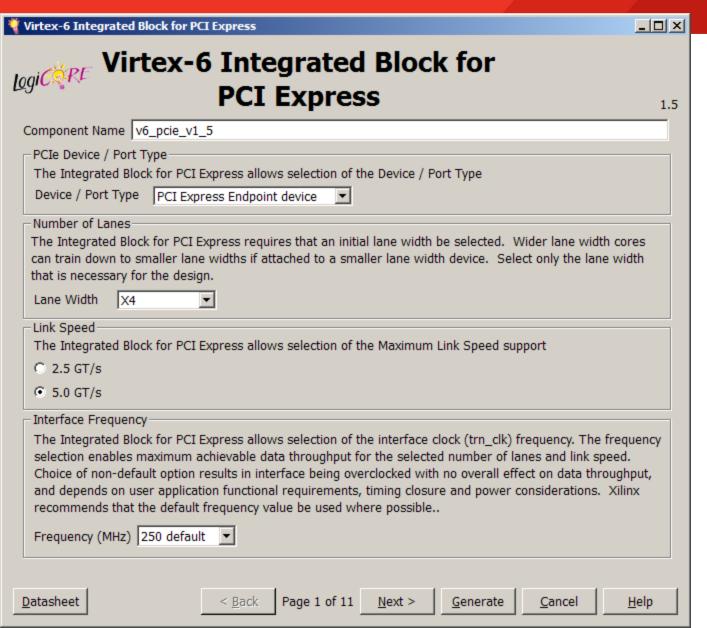

#### Select

Virtex-6 Integrated Block for PCI Express, Version 1.5

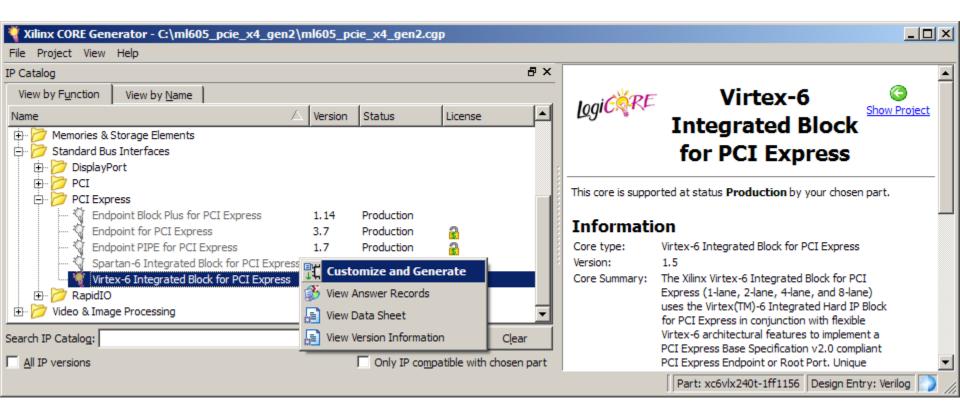

- Right click on the Virtex-6 Integrated Block for PCI Express,

Version 1.5

- Select Customize and Generate

- Set the laneWidth to X4

- Set the LinkSpeed to 5.0GT/s

- Click Next

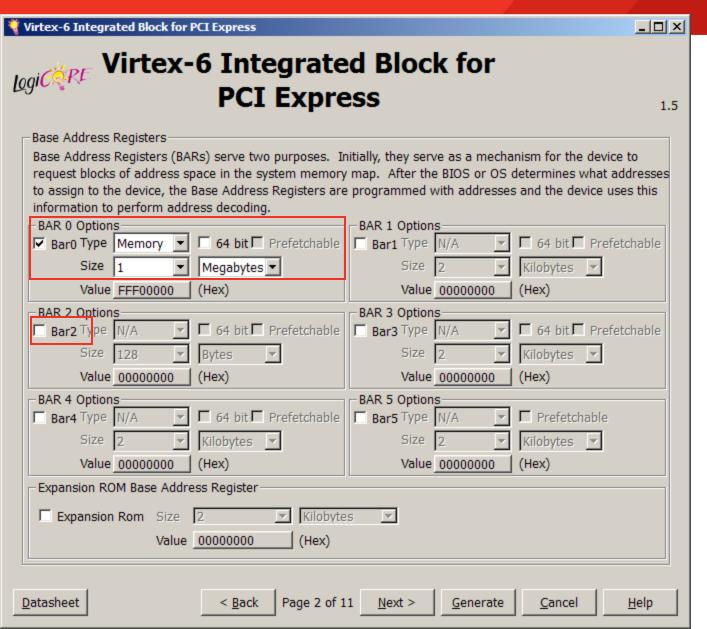

- BAR 0

- Set to 1Megabytes

- BAR 2

- Deselect BAR 2

- Click Next

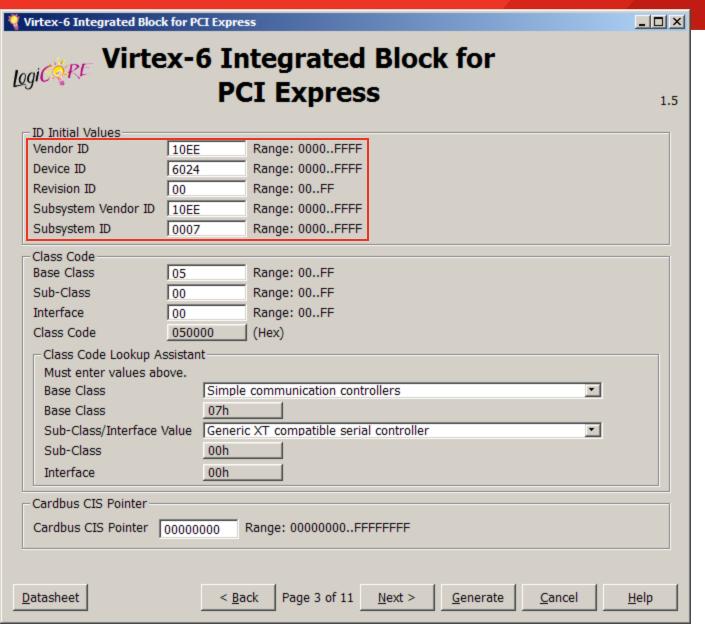

- Note ID Initial Values

- Vendor ID = 10EE

- Device ID = 6024

- Revision ID = 00

- SubsystemVendor ID =10EE

- Subsystem ID =0007

- Click Next 6 times

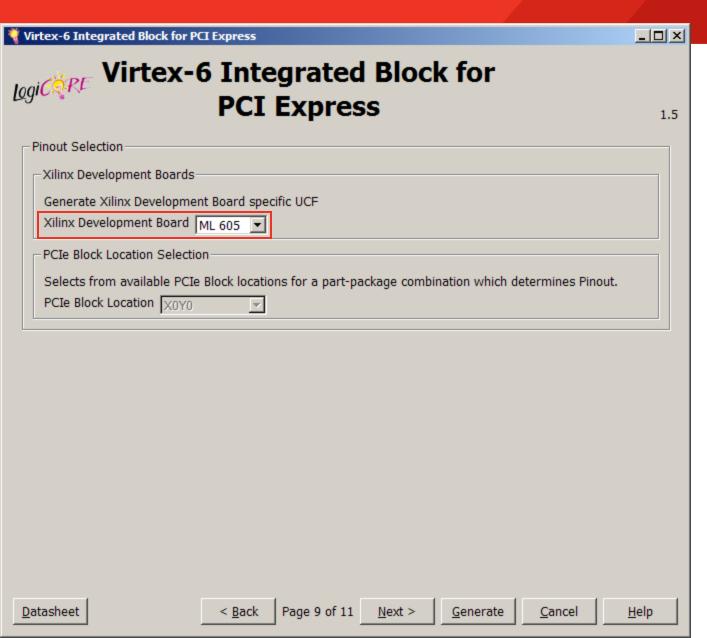

- On Page 9

- Select ML605

- Click Generate

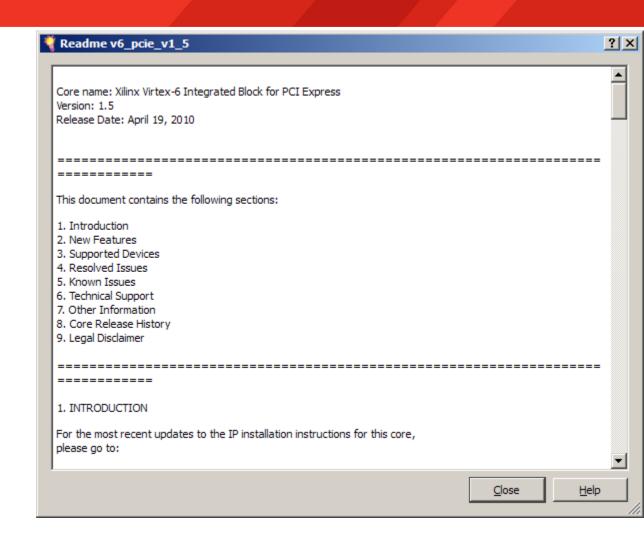

After the PCle core finishes generating, click Close on the Readme File window

■ The v6\_pcie\_v1\_5 IP appears under the Project IP tab

### **Compile PCIe Core**

Type these commands in a windows command shell:

cd C:\ml605\_pcie\_x4\_gen2\v6\_pcie\_v1\_5\implement implement.bat > implement.log 2>&1

```

Microsoft Windows XP [Version 5.1.2600]

(C) Copyright 1985-2001 Microsoft Corp.

C:\>cd C:\m1605_pcie_x4_gen2\v6_pcie_v1_5\implement

C:\m1605_pcie_x4_gen2\v6_pcie_v1_5\implement>implement.bat > implement.log 2>&1

```

### **Create PCIe ACE File (Optional)**

Type these commands in a windows command shell:

cd C:\ml605\_pcie\_x4\_gen2\ready\_for\_download make\_ace.bat

```

C:\command Prompt

Microsoft Windows XP [Version 5.1.2600]

(C) Copyright 1985-2001 Microsoft Corp.

C:\cd C:\m1605_pcie_x4_gen2\ready_for_download

C:\m1605_pcie_x4_gen2\ready_for_download>make_ace.bat

```

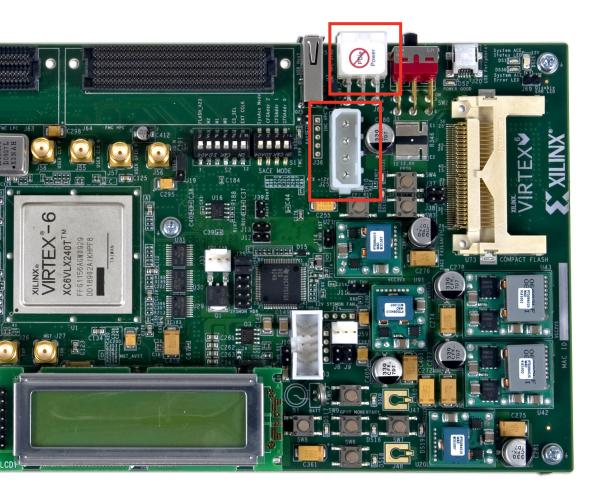

- Power on the ML605

- Connect a USB Type-A to Mini-B cable to the USB JTAG connector on the ML605 board

- Connect this cable to your PC

- Set S2 to 011001 (1 = on, Position 6 → Position 1)

- This selects Slave SelectMAP (Positions 5, 4, and 3), Platform Flash (2) and EXT CCLK (1, for PCIe compliance)

- Set S1 to 0XXX (X = Don't care, Position 4 → Position 1)

- This disables the Compact Flash

#### Run iMPACT:

#### impact

```

Microsoft Windows XP [Version 5.1.2600]

(C) Copyright 1985-2001 Microsoft Corp.

C:\>cd C:\m1605_pcie_x4_gen2\v6_pcie_v1_5\implement

C:\m1605_pcie_x4_gen2\v6_pcie_v1_5\implement\results\rimpact

C:\m1605_pcie_x4_gen2\v6_pcie_v1_5\implement\results\rimpact

```

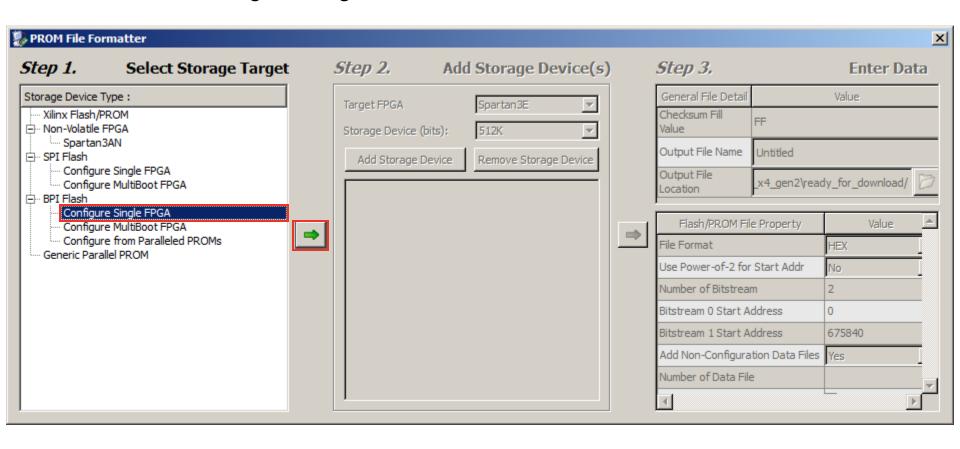

#### Select

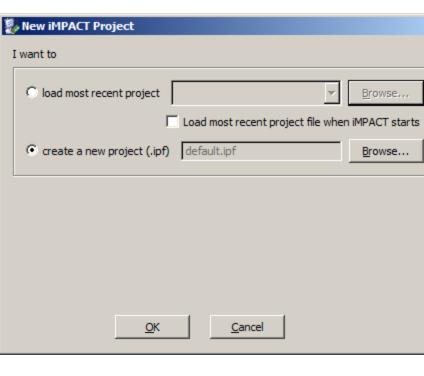

- Create a new project

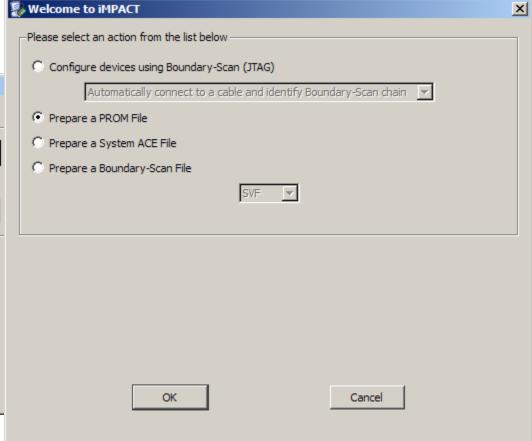

- Prepare a PROM File

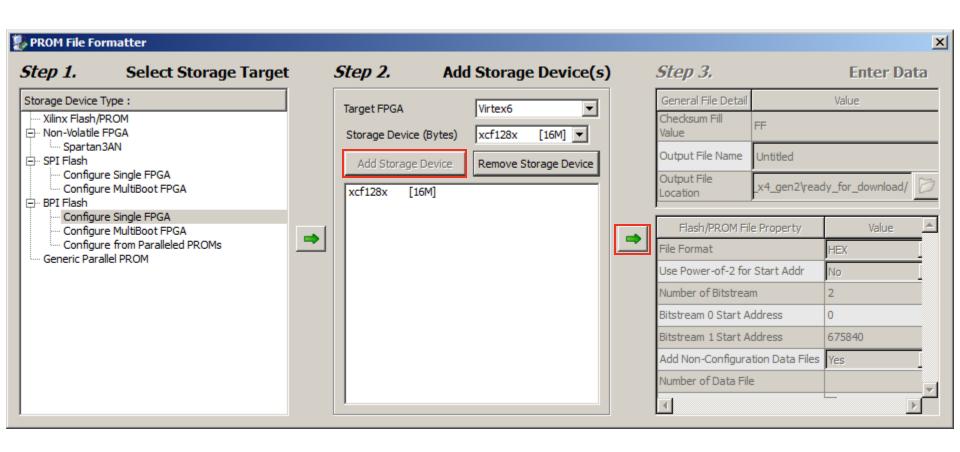

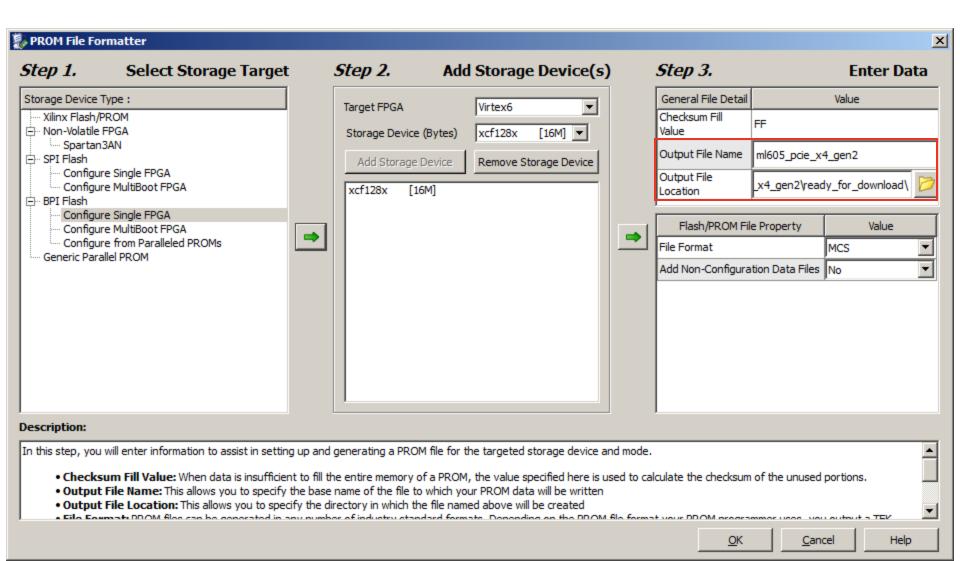

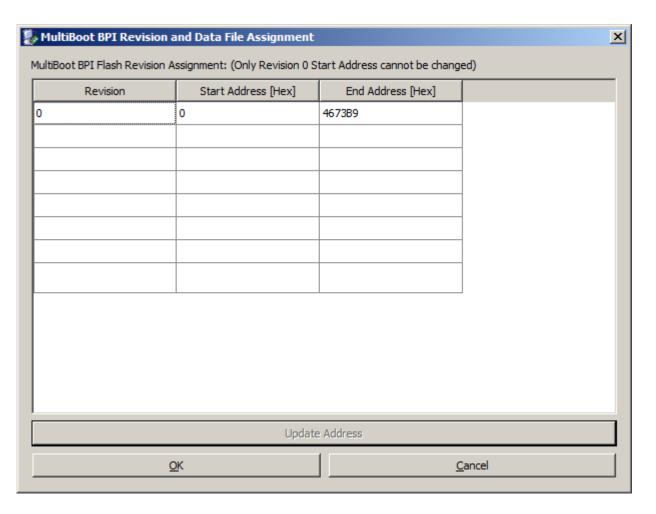

- To generate a PROM file for the XCF128X Platform Flash, select:

- BPI Configure Single FPGA

Add xcf128x

Set file name and location as desired and click OK

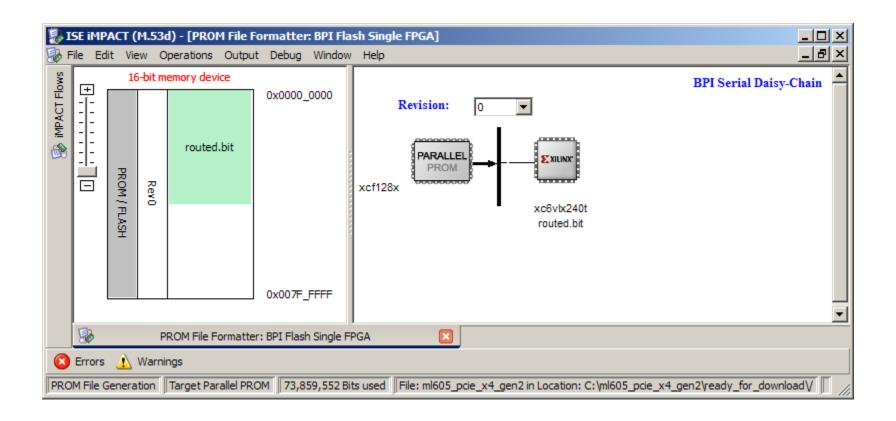

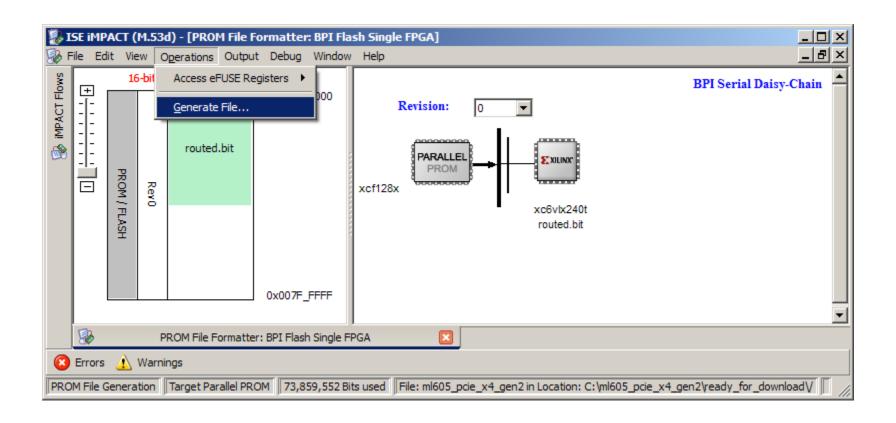

Add routed.bit from the <design path>\v6\_pcie\_v1\_5\implement\results

Click OK on this dialog

From the iMPACT menu, select

**Operations** → **Generate File...**

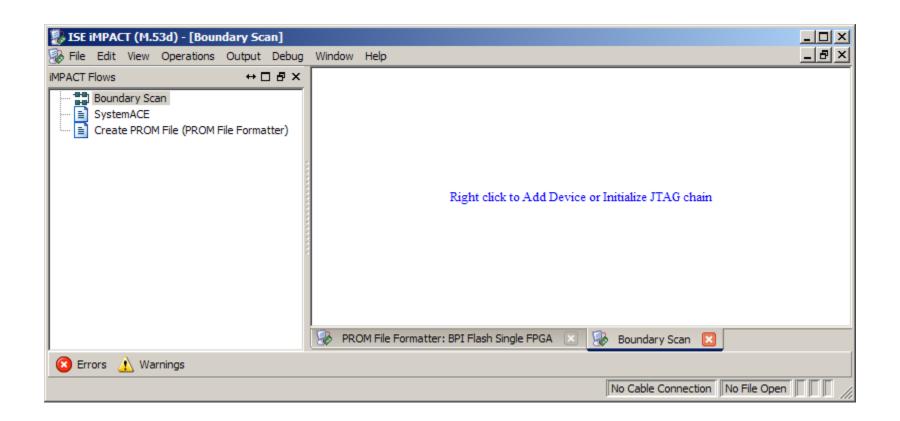

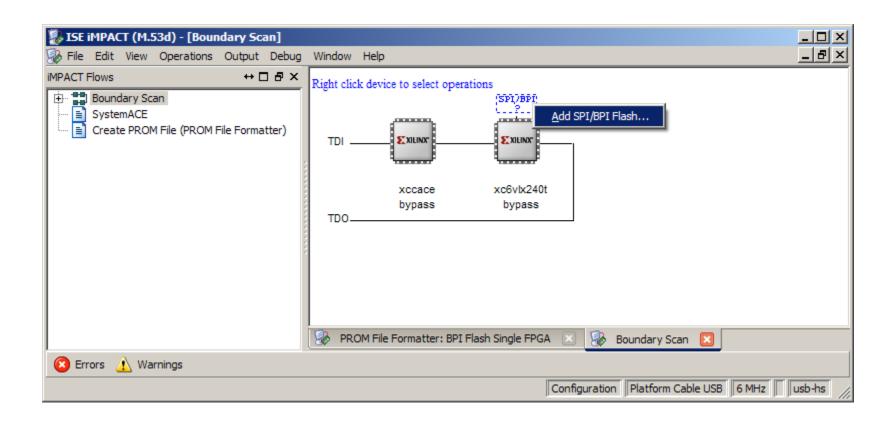

After generation completes, under the iMPACT Flows, double click on Boundary Scan

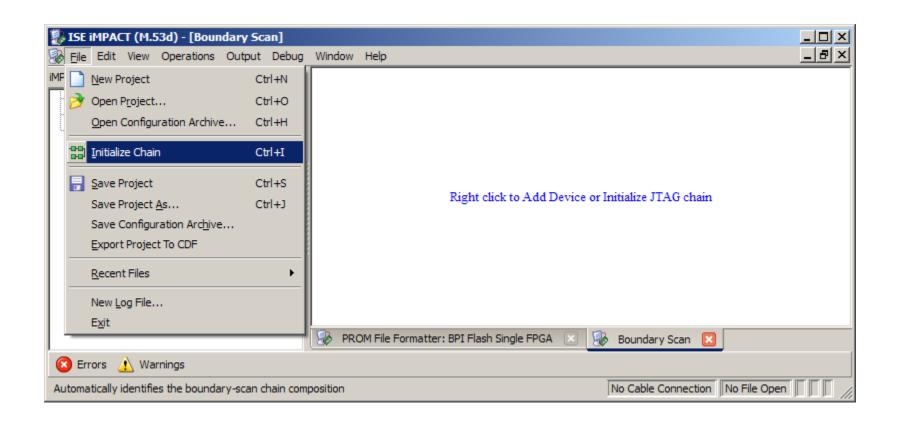

From the iMPACT menu, select

File → Initialize Chain

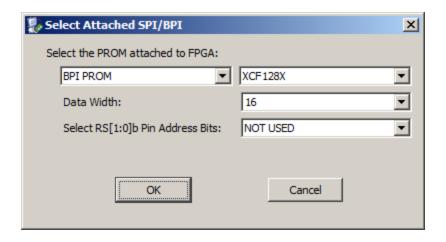

- Right click on the SPI/BPI ? and select Add SPI/BPI Flash…

- Add <design path>\ready\_for\_download\ml605\_pcie\_x4\_gen2.mcs

Click OK for this dialog

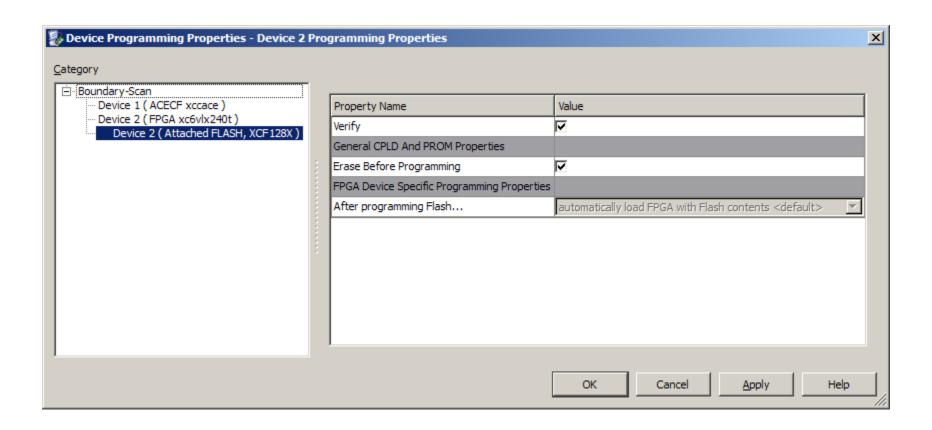

- Right click on the Flash and select Program

- Use default settings to Erase and Verify device

Erase Before Programming must be selected

## **Hardware Setup**

- Insert the ML605 Board into a PCle x4 slot (x16 shown)

- Connect PC power to J25, turn on Power Switch

# **Hardware Setup**

Do not use the PCle connector from the PC power supply

#### **Hardware Setup**

■ Do not connect both the ML605 power brick connector (J60) and

the four pin ATX power connector at the same time

- Power on the PC

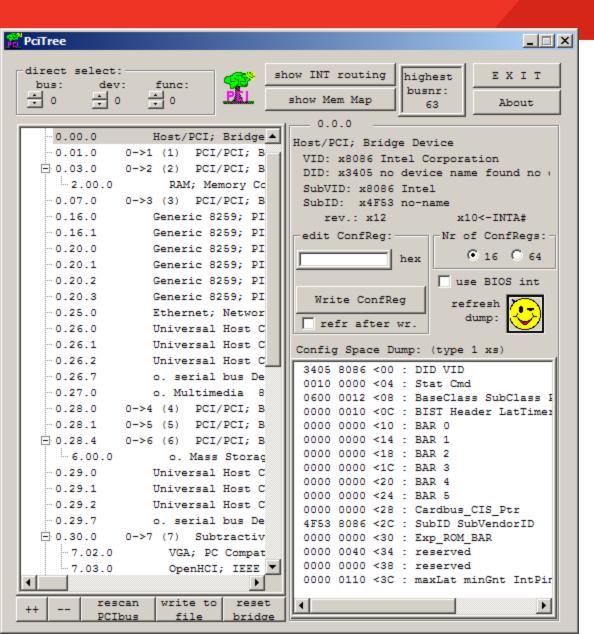

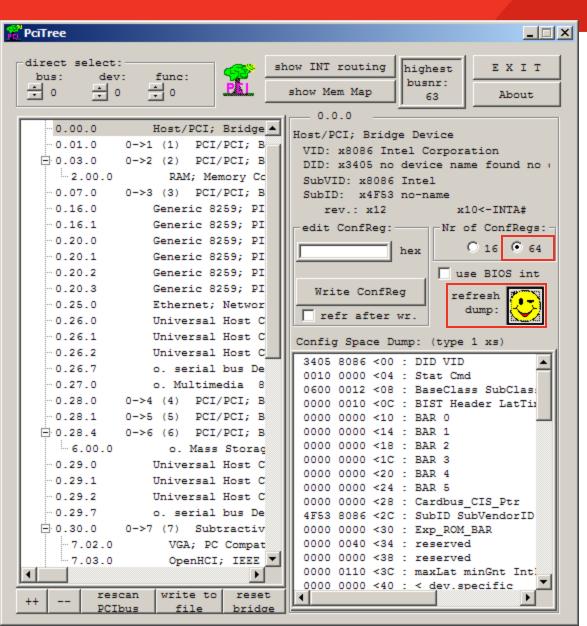

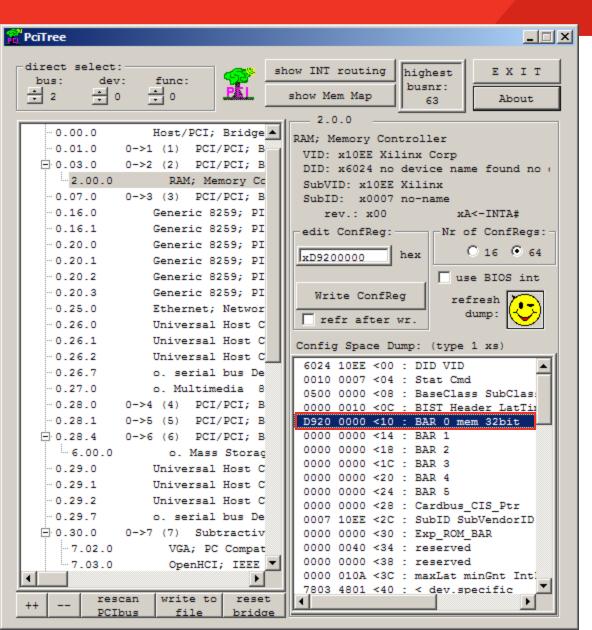

- Start PciTree

- Set Number of Configuration Registers to 64

- Click on Refresh dump

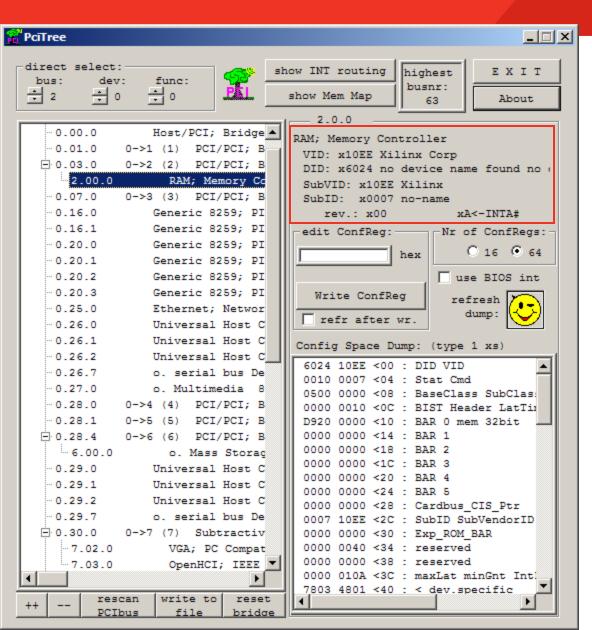

- Locate the Xilinx Device

- Vendor ID is 0x10EE

- The x4 Gen2 configuration will have a Device ID of 0x6024

- Navigate the linked list in configuration space to locate the PCIe

Capabilities Structure

- See <u>UG517</u> for details

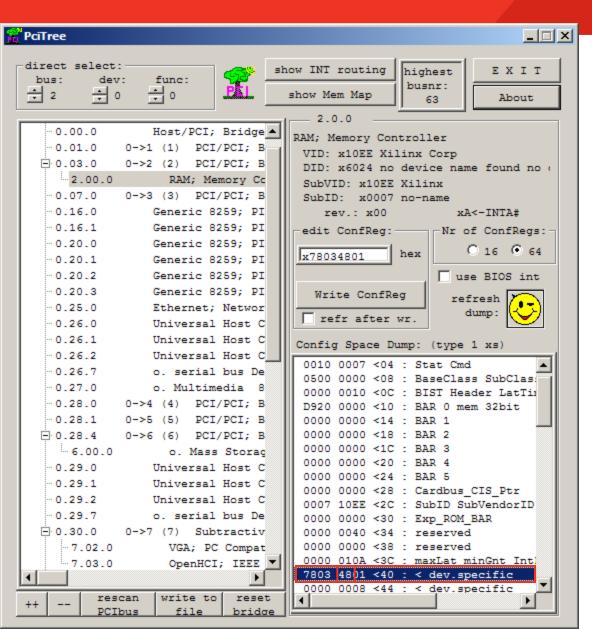

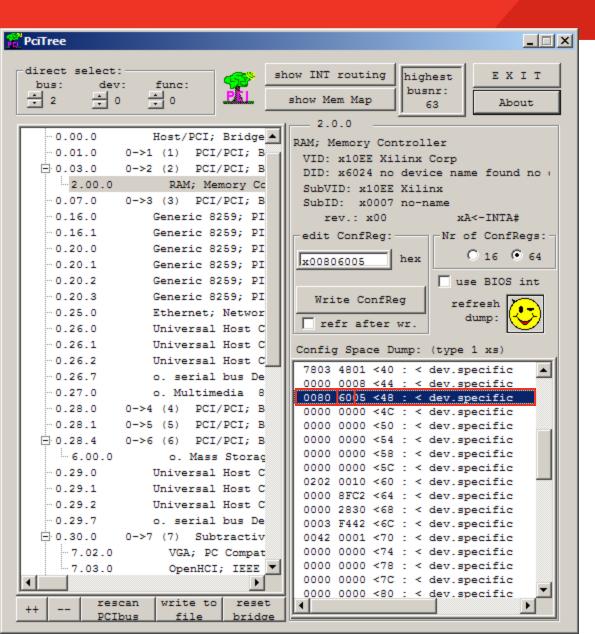

- With the Xilinx device selected, select Register 0x40

- Register 0x40 points to the next structure

- 0x48 is the address of the next structure

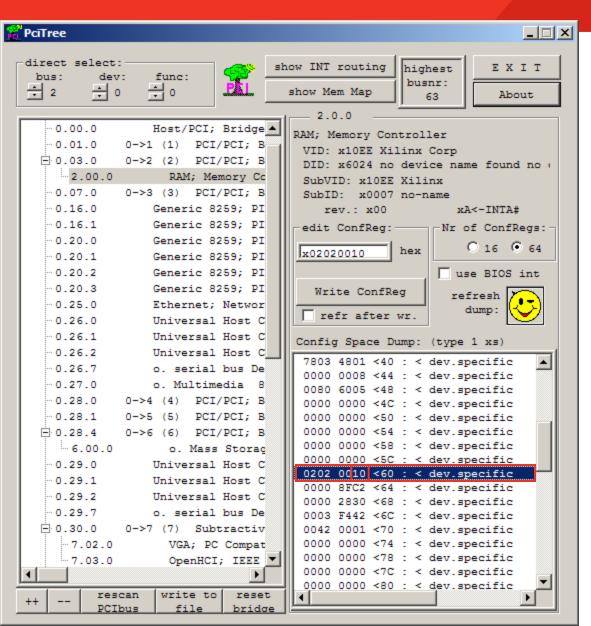

#### Select Register 0x48

- Register 0x48 points to the next structure

- 0x60 is the address of the next structure

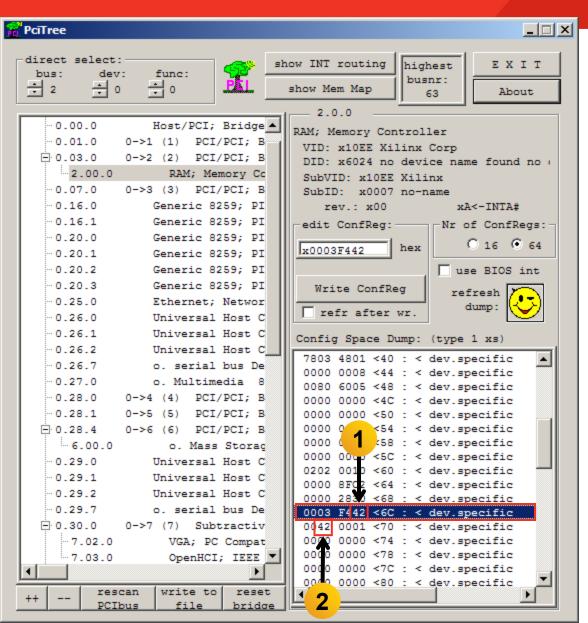

#### Register 0x60

- 0x60 is a type 0x10,

indicating PCIe

Capabilities Structure

- Last Structure

#### Register 0x6C

- Link Capabilities Register

- Indicates the maximum number of lanes and speed (Gen1, Gen2) for device

- The value 0x42 shows this is an x4 Gen2 device (1)

#### Link Status Register

- -0x70

- Shows the current link status

- This design, in a Gen2 chassis, trained to x4 Gen2 (2)

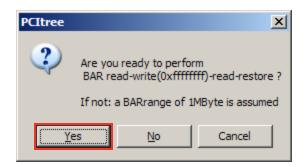

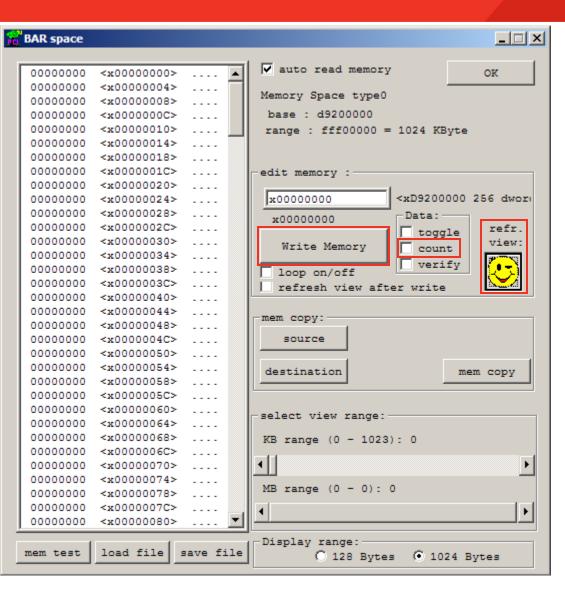

- Double-click on BAR 0

- BAR 0 Address is machine dependent

- Click Yes on the Dialog box seen below

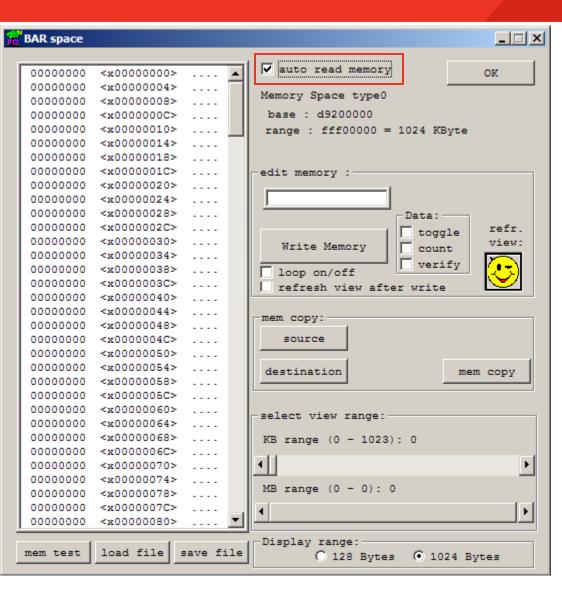

Select auto read memory

- Click on the first memory location

- Type <Shift-End> to select 1024 Bytes

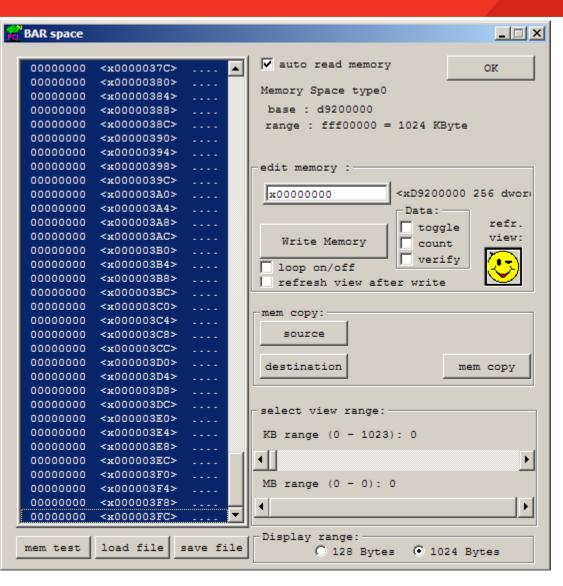

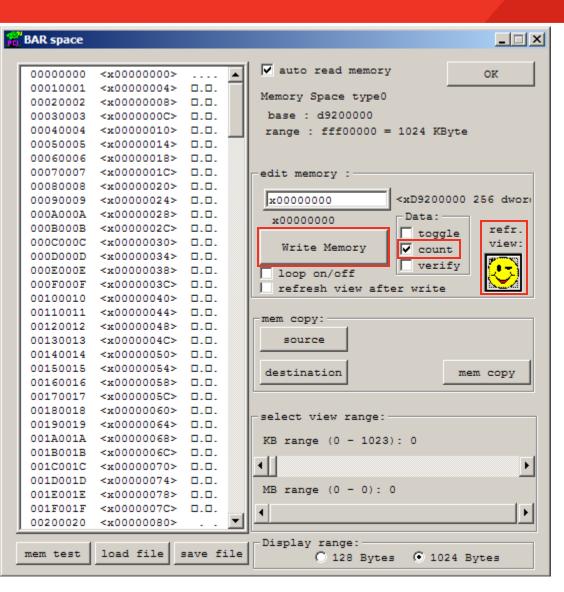

- Write Memory

- Select count

- Click Write Memory

- Click refr view

- View results counting up to FF

- Restore Memory

- Deselect count

- Click Write Memory

- Click refr view

- Memory is reset to zeros

#### Virtex-6 PCIe x4 Gen2 Capability

- ML605 Supports PCIe Gen1 and Gen2 Capability

- x4, x2, or x1 Gen2 lane width

- x8 Gen2 not supported in -1 parts

- LogiCORE PIO Example Design

- RDF0009.zip

- Available through http://www.xilinx.com/ml605

- LogiCORE Integrated Block for PCI Express

- See <u>UG517</u> for details

# References

#### References

#### PCIe Base Specification

PCI SIG Web Site<a href="http://www.pcisig.com/home">http://www.pcisig.com/home</a>

#### Virtex-6 PCIe

- PCIe Product Overview

<a href="http://www.xilinx.com/products/ipcenter/V6">http://www.xilinx.com/products/ipcenter/V6</a> PCI Express Block.htm

- Virtex-6 FPGA Integrated Block v1.5 for PCI Express User Guide

<a href="http://www.xilinx.com/support/documentation/ip\_documentation/v6\_pcie\_ug517.pdf">http://www.xilinx.com/support/documentation/ip\_documentation/v6\_pcie\_ug517.pdf</a>

- Virtex-6 FPGA Integrated Block v1.5 for PCI Express Data Sheet

<a href="http://www.xilinx.com/support/documentation/ip documentation/v6 pcie ds715.pdf">http://www.xilinx.com/support/documentation/ip documentation/v6 pcie ds715.pdf</a>

- IP Release Notes Guide

http://www.xilinx.com/support/documentation/ip documentation/xtp025.pdf

# **Documentation**

#### **Documentation**

#### Virtex-6

Virtex-6 FPGA Family

<a href="http://www.xilinx.com/products/virtex6/index.htm">http://www.xilinx.com/products/virtex6/index.htm</a>

#### ML605 Documentation

- Virtex-6 FPGA ML605 Evaluation Kit

<a href="http://www.xilinx.com/products/devkits/EK-V6-ML605-G.htm">http://www.xilinx.com/products/devkits/EK-V6-ML605-G.htm</a>

- ML605 Hardware User Guide

<a href="http://www.xilinx.com/support/documentation/boards">http://www.xilinx.com/support/documentation/boards</a> and kits/ug534.pdf

- ML605 Reference Design User Guide

http://www.xilinx.com/support/documentation/boards and kits/ug535.pdf