# Agilent Logic and Protocol Analyzer

**User Guide**

# Notices

© Agilent Technologies, Inc. 2001-2014

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

#### **Trademarks**

ARM® and Thumb® are registered trademarks and ARM7TDMI(TM) is a trademark of ARM Limited.

Intel® and Pentium® are U.S. registered trademarks of Intel Corporation.

Java(TM) is a U.S. trademark of Sun Microsystems, Inc.

#### **Software Release version**

Version 05.80.0000

#### **Edition**

February 2014

Available in electronic format only

Agilent Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

#### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

#### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

#### **Safety Notices**

#### CAUTION

A **CAUTION** notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a **CAUTION** notice until the indicated conditions are fully understood and met.

### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

# Using the Agilent Logic and Protocol Analyzer

The Agilent Logic and Protocol Analyzer application is used with:

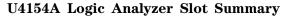

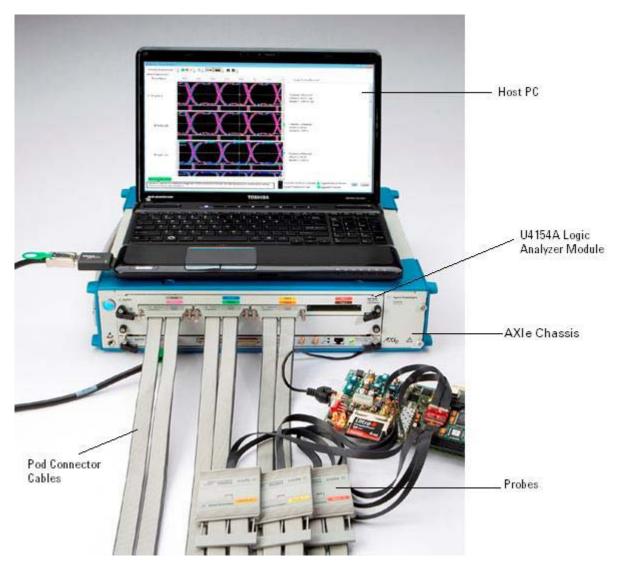

- modules in Agilent AXIe chassis (for example the U4154A Logic Analyzer module in M9502A portable 2-slot chassis)

- modules in Agilent Digital Test Console chassis (for example the U4002A portable 2-slot chassis)

- 16900-series logic analysis systems (see page 617), 16800-series logic analyzers (see page 614), and 1680/1690-series logic analyzers (see page 608) and 16850-series logic analyzers.

- It can also be used by itself on a Windows XP/Vista/7/8 computer for *remote access* (see page 85) of logic analysis systems on the network, or for *offline analysis* (see page 233) of captured data (including data captured on 16700-series logic analyzers).

This online help provides the following information.

- What's New (see page 19)

- Getting Started (see page 59)

- Probing the Device Under Test (see page 81)

- Connecting to a Logic Analysis System (see page 85)

- Setting Up the Logic Analyzer (see page 97)

- Configuring Logic Analyzer Modules (see page 98)

- "Setting Up Probes" (in the online help)

- Setting the Logic Analyzer Threshold Voltage (see page 102)

- Defining Buses and Signals (see page 104)

- Choosing the Sampling Mode (see page 119)

- Setting Up Symbols (see page 139)

- Installing Licensed Hardware Upgrades (see page 147)

- Capturing Data from the Device Under Test (see page 149)

- Setting Up Quick (Draw Box) Triggers (see page 152)

- Specifying Simple Triggers (see page 156)

- Specifying Advanced Triggers (see page 163)

- Triggering From, and Sending Triggers To, Other Modules/Instruments (see page 193)

- Storing and Recalling Triggers (see page 201)

- Running/Stopping Measurements (see page 203)

- Saving Captured Data (and Logic Analyzer Setups) (see page 205)

- Extending Capture Capability with VBA (see page 217)

- Analyzing the Captured Data (see page 219)

- Offline Analysis (see page 233) (after Loading Saved Data and Setups (see page 220))

- Analyzing Waveform Data (see page 239)

- Analyzing Listing Data (see page 259)

- Displaying Names (Symbols) for Bus/Signal Values (see page 269)

- Marking, and Measuring Between, Data Points (see page 271)

- Searching the Captured Data (see page 294)

- Comparing Captured Data to Reference Data (see page 305)

- Viewing Source Code Associated with Captured Data (see page 308)

- Analyzing Packet Data (see page 316)

- Analyzing the Same Data in Different Ways (Using the Window) (see page 345)

- Setting the System Trigger and Skew Between Modules (see page 351)

- Using Display Windows (see page 353)

- Printing Captured Data (see page 354)

- Extending Data Visualization/Analysis with VBA (see page 357)

- "Using Tools" (in the online help)

- "External Oscilloscope Time Correlation and Data Display" (in the online help)

- "Using the Pattern Generator" (in the online help)

- "Using the PCIe Gen3 Analyzer"

- Managing Software Licenses (see page 359)

- Updating Software (see page 367)

- Solving Problems (see page 371)

- Concepts (see page 409)

- **Reference** (see page 451)

- Glossary (see page 787)

- "COM Automation" (in the online help)

- "XML Format" (in the online help)

- See Also > "AXIe Based Logic Analysis and Protocol Test Modules Installation Guide"

- , "16900-Series Logic Analysis System Installation Guide"

- Installation/Quick Start Guide

- "1680-Series Logic Analyzers Quick Start/Installation Guide"

- Image: "I690-Series Logic Analyzers Quick Start/Installation Guide"

- > "16850-Series Logic Analyzers Installation/Quick Start Guide"

# Contents

Using the Agilent Logic and Protocol Analyzer 3

#### 1 What's New

| ew                       |    |

|--------------------------|----|

| Version 05.70 What's New | 21 |

| Version 05.60 What's New | 23 |

| Version 05.50 What's New | 25 |

| Version 05.40 What's New | 27 |

| Version 05.30 What's New | 29 |

| Version 05.20 What's New | 31 |

| Version 05.00 What's New | 34 |

| Version 04.00 What's New | 36 |

| Version 03.83 What's New | 37 |

| Version 03.82 What's New | 39 |

| Version 03.80 What's New | 40 |

| Version 03.70 What's New | 41 |

| Version 03.67 What's New | 43 |

| Version 03.65 What's New | 44 |

| Version 03.60 What's New | 45 |

| Version 03.55 What's New | 46 |

| Version 03.50 What's New | 47 |

| Version 03.30 What's New | 49 |

| Version 03.20 What's New | 51 |

- Version 03.00 What's New 52

- Version 02.50 What's New 53

- Version 02.00 What's New 54

- Version 01.40 What's New 55

- Version 01.20 What's New 57

- Version 01.10 What's New 58

#### **2 Getting Started**

| Tutorial - Getting to know your logic analyzer 60  |

|----------------------------------------------------|

|                                                    |

| Turning on the logic analyzer 61                   |

| Connecting to the device under test 61             |

| Setting up bus/signal names 62                     |

| Setting the acquisition mode 64                    |

| Setting up a simple trigger 64                     |

| Open the tutorial configuration file 65            |

| Using markers 66                                   |

| Zooming in on the data 67                          |

| Loading and saving configuration files 67          |

| Saving and recalling trigger setups 68             |

| Quick marker measurements 69                       |

| Searching data 70                                  |

| Toolbars, tool tips, and mouse shortcuts 71        |

| Measurement Examples 72                            |

| Making a timing analyzer measurement 72            |

| Making a state analyzer measurement 73             |

| To trigger on one of multiple edges or glitches 74 |

| To trigger on ranges 75                            |

|                                                    |

| Demo Center 78                                     |

#### **3** Probing the Device Under Test

To control signals in the device under test 83

#### **4** Connecting to a Logic Analysis System

Connecting to the U4154A Logic Analyzer Module85To add a logic analysis system to the list87To delete a logic analysis system from the list88To refresh the logic analysis system list89To view logic analysis system details90

To enter your "System In Use" comments 91

To select a logic analysis system for auto-connect 92

To chat with another logic analysis system user 93

Setting Up Passwords for Remote Access 94

#### **5** Setting Up the Logic Analyzer

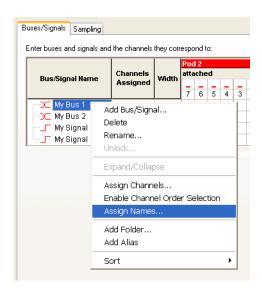

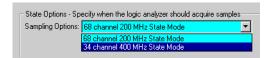

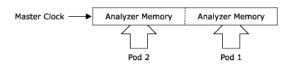

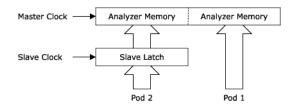

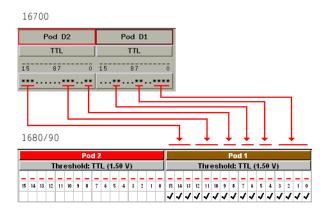

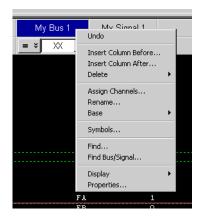

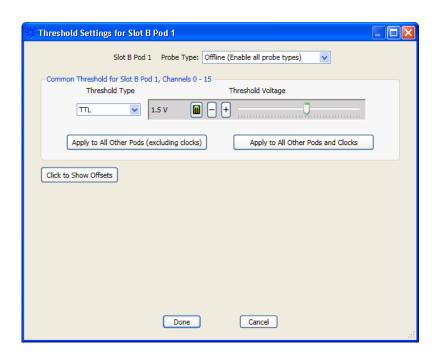

**Configuring Logic Analyzer Modules** 98 To disable and enable modules 98 To unsplit a split analyzer 100 Setting the Logic Analyzer Threshold Voltage 102 **Defining Buses and Signals** 104 To add a new bus or signal 105 To delete a bus or signal 106 To rename a bus or signal 107 To rename the bits of a bus 108 To assign channels in the default bit order 110 To assign channels, selecting the bit order 111 To use clock channels as extra data channels 112 To define buses and signals by importing netlist files 113 To reorder bits by editing the Channels Assigned string 114 To set the default number base 116 To set polarity 117 To add user comments 117 To add a folder 118 To alias a bus/signal name 118 To sort bus/signal names 118 Choosing the Sampling Mode 119 Selecting the Timing Mode (Asynchronous Sampling) 120 Selecting the State Mode (Synchronous Sampling) 122 In Either Timing Mode or State Mode 134 Using Timing Zoom 136 Setting Up Symbols 139 To create user-defined symbols 139 To load symbols from a file 141 To run the symbol reader outside the application 142 To create an ASCII symbol file 143 To change symbol reader options 143 To enter symbolic bus/signal values 146 Installing Licensed Hardware Upgrades 147

#### 6 Capturing Data from the Device Under Test

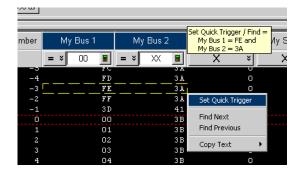

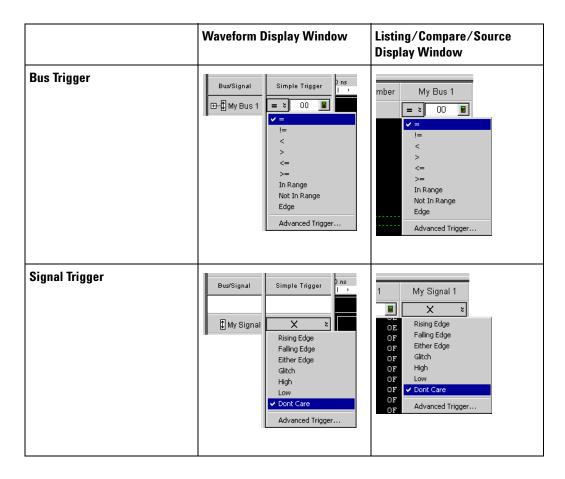

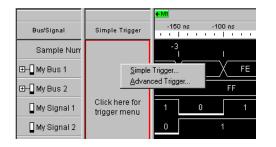

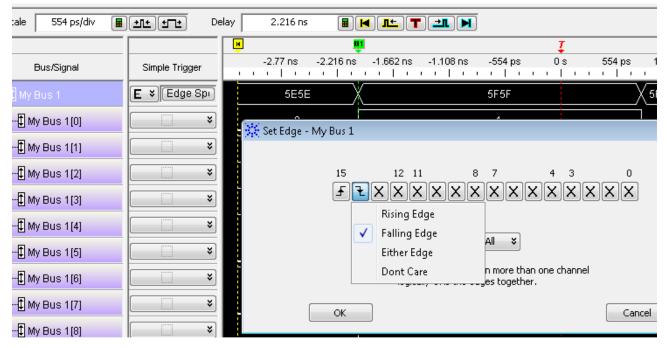

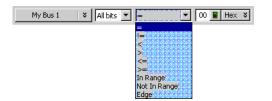

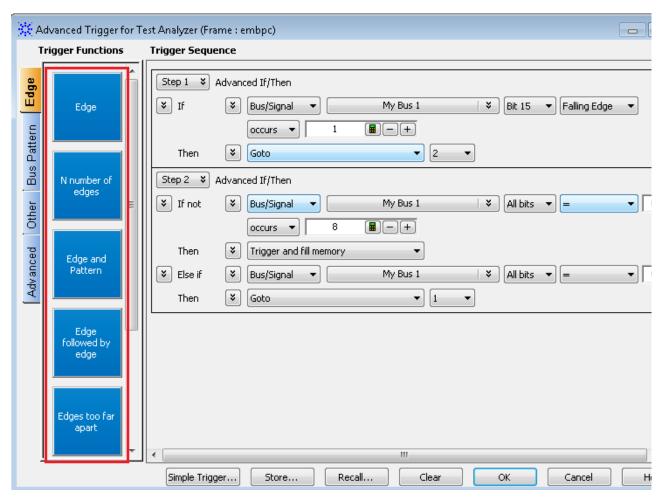

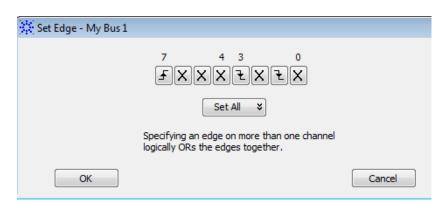

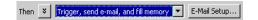

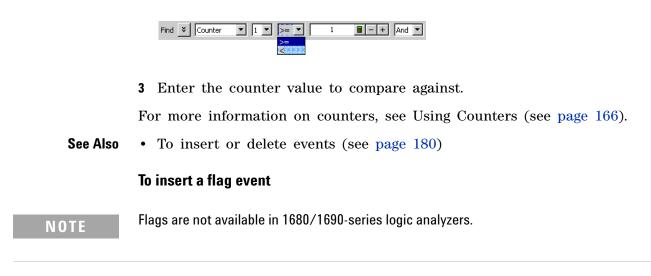

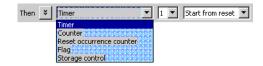

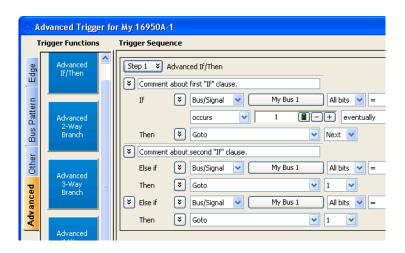

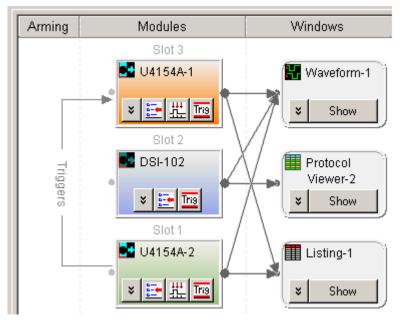

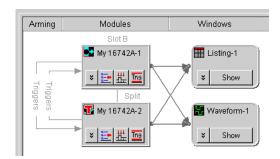

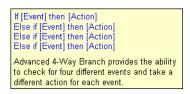

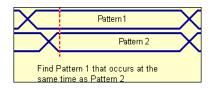

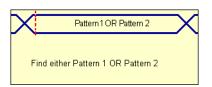

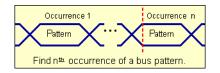

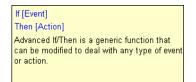

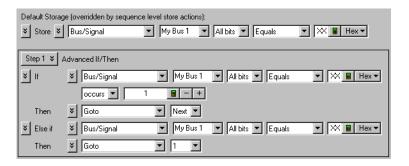

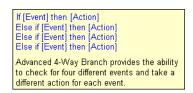

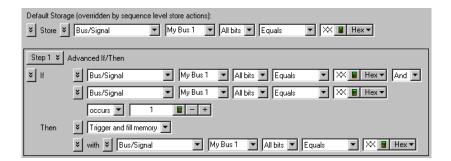

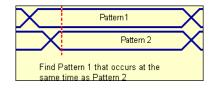

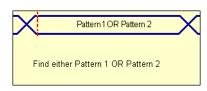

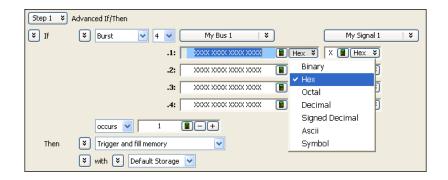

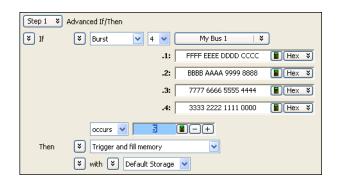

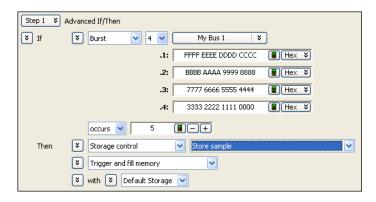

Setting Up Quick (Draw Box) Triggers 152 To set a Quick Trigger in the Waveform window 152 153 To set a Quick Trigger in the Listing window 154 To set a Quick Trigger in the Source window **Specifying Simple Triggers** 156 To specify bus patterns in a simple trigger 157 158 To specify signal levels in a simple trigger To set a bus/signal edge in a simple trigger 159 Specifying Advanced Triggers 163 **Reading Event and Action Statements** 165 Using Timers 165 Using Counters 166 **Using Flags** 167 To replace or insert trigger functions into trigger sequence steps 169 To specify bus/signal patterns 169 To set a bus/signal edge in an advanced trigger 171 To specify packet events (in "Find a packet" trigger function) 175 To specify a trigger sequence step's goto or trigger action 178 To specify default storage 179 To insert or delete events 180 To negate events 183 To change the evaluation order of AND/OR'ed events 184 To choose between a duration or occurrence count for events (timing mode) 184 To insert or delete actions (in a trigger sequence step) 185 To cut, copy, and paste trigger sequence steps 188 To delete trigger sequence steps 189 To show a trigger sequence step as Advanced If/Then trigger functions 189 To convert a trigger sequence step to Advanced If/Then trigger functions 190 To display or hide "If" clause comments 190 To clear the trigger sequence 192 Triggering From, and Sending Triggers To, Other Modules/Instruments 193 To arm one module with another module's trigger 193 To trigger other instruments - Trigger Out 198 To trigger analyzer from another instrument - Trigger In 199 **Storing and Recalling Triggers** 201 To store a trigger 201 To recall a trigger 202 To set the trigger history depth 202

| Running/Stopping Measurements 203                      |

|--------------------------------------------------------|

| To change the "Go to Trigger on Run" option 204        |

| Saving Captured Data (and Logic Analyzer Setups) 205   |

| To save a configuration file 206                       |

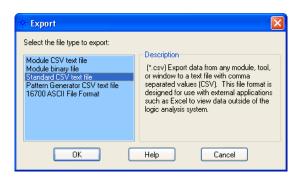

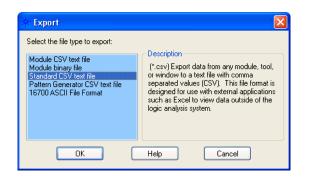

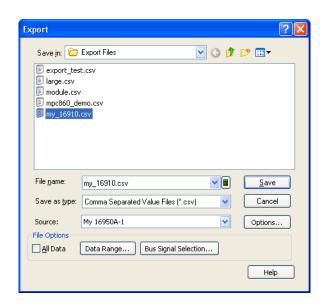

| To export data to standard CSV format files 207        |

| To export data to module CSV format files 210          |

| To export data to module binary (ALB) format files 213 |

| To export data to 16700 ASCII format files 215         |

| Extending Capture Capability with VBA 217              |

7 Analyzing the Captured Data

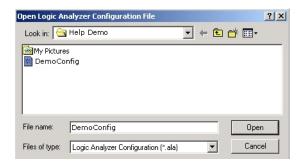

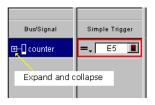

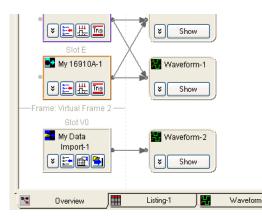

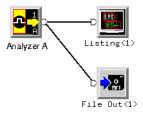

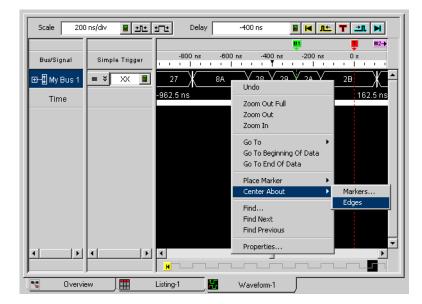

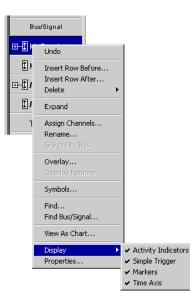

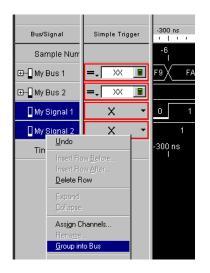

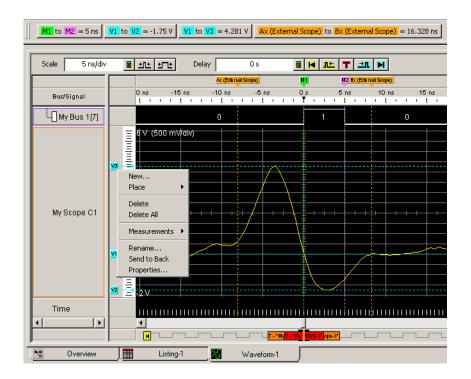

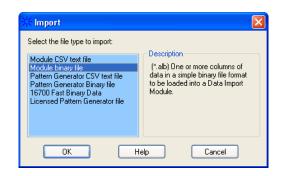

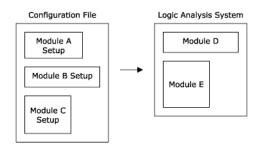

220 Loading Saved Data and Setups 220 To open a configuration file To recall a recently used configuration file 222 To import 167xx fast binary data 223 To transfer module setups to/from multi-module systems 224 To set up multiple-modules with XML-format configurations 224 Using Data Import Modules 227 **Offline Analysis** 233 Analyzing 16700-Series Logic Analyzer Data 234 Offline Analysis on Logic Analyzers 235 **Offline Analysis on Personal Computers** 236 **Offline File Formats** 237 Analyzing Waveform Data 239 240 To change the display scale (time/division) To go to different locations in the captured data 242 To re-arrange waveforms 243 244 To overlay waveforms To find a bus/signal row 244 To view bus data as a chart 245 To show/hide parts of the waveform display 247 To insert or delete buses/signals 247 248 To group signals into a bus To expand/collapse buses 248 To insert separator rows 248 **Changing Waveform Window Properties** 249 253 Changing Bus/Signal Row Properties **Changing Analog Signal Row Properties** 256

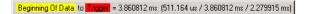

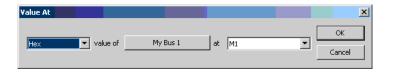

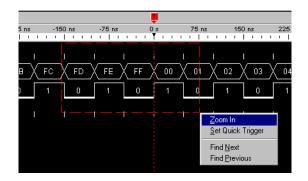

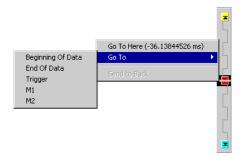

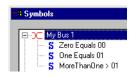

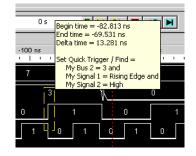

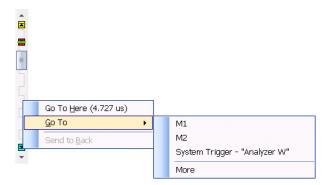

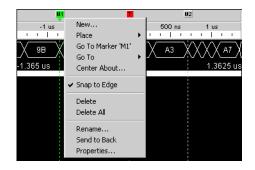

Analyzing Listing Data 259 To go to different locations in the captured data 260 To re-arrange bus/signal columns 261 To find a bus/signal column 261 To show/hide parts of the listing display 262 To insert or delete buses/signals 262 **Changing Listing Window Properties** 263 **Changing Bus/Signal Column Properties** 265 Displaying Names (Symbols) for Bus/Signal Values 269 Marking, and Measuring Between, Data Points 271 To read the markers display and overview bars 272 To create new markers 272 To place markers in data 274 276 To go to a marker To center the display about a marker pair 277 To change a marker's snap to edge setting 277 To delete a marker 278 To create a new time interval measurement 279 To create a new sample interval measurement 280 To create a new value at measurement 282 To rename a marker 282 To send a marker to the back 283 **Changing Marker Properties** 284 Using Voltage Markers for Analog Signals (in the Waveform Display) 286 Searching the Captured Data 294 To quickly find bus/signal patterns 294 To find bus/signal patterns in the captured data 296 298 To find packet patterns in the captured data To find complex patterns in the captured data 302 To store, recall, or delete favorite find patterns 303 To specify "found" marker placement 304 **Comparing Captured Data to Reference Data** 305 To copy data to the reference buffer 305 To find differences in the compared data 306 306 To compare only a range of samples To offset the reference data 306 To run until a number of compare differences 307 To set Compare window properties 307

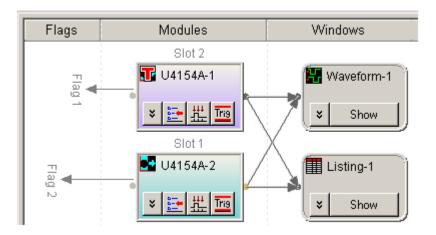

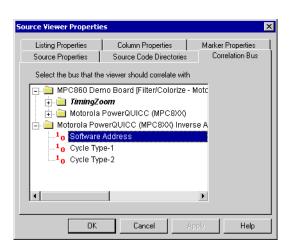

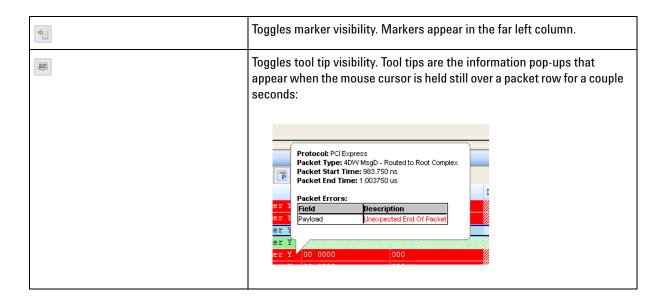

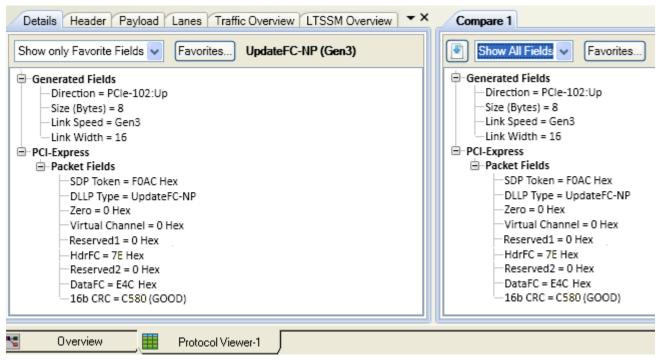

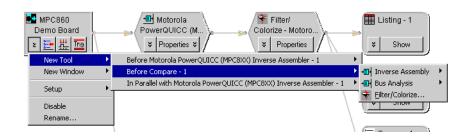

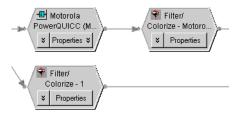

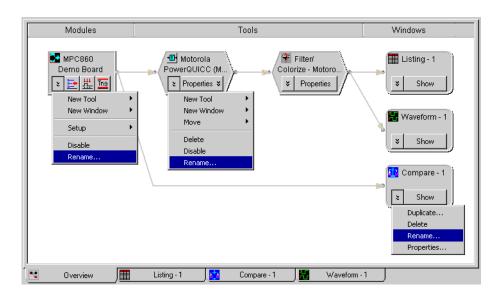

308 Viewing Source Code Associated with Captured Data To step through captured data by source lines 309 To go to captured data associated with a source line 309 310 To browse source files To search for text in source files 310 To go to the source line associated with the listing center rectangle 311 To edit the source code directory list 311 To select the correlation bus 312 **Changing Source Window Properties** 313 Analyzing Packet Data 316 Viewing the Packet Summary 319 Viewing a Selected Packet 328 **Changing Packet Summary Event Colors** 337 **Changing Protocol Viewer Window Properties** 338 340 **Changing Packet Summary Column Properties** Analyzing the Same Data in Different Ways (Using the Overview Window) 345 To open or display the Overview window 345 To add, duplicate, or delete windows and tools 346 To edit window or tool properties 348 To rename windows, tools, and modules 349 To redraw the Overview window 350 To delete the Overview window 350 Setting the System Trigger and Skew Between Modules 351 **Using Display Windows** 353 To add or delete display windows 353 To turn window tabs on/off 353 354 **Printing Captured Data** To print captured data 354 To copy text to the clip board 355 To copy a screen to the clip board 355 To install a printer 355 355 To connect a LAN Extending Data Visualization/Analysis with VBA 357 8 Managing Software Licenses To view active software license information 360 To activate software licenses 361

To access floating license servers 362

To borrow floating licenses and return them early 364

#### 9 Updating Software

#### **10 Solving Problems**

**Software Installation Problems** 372 Installation Errors on 1680-Series Logic Analyzers 372 If starting in offline mode is unexpected 373 If an ALA format configuration file won't open 374 Interpreting Error Messages 375 **Error Messages** 375 Warning Messages 386 **Informational Messages** 388 Eye Finder Info Messages 388 License Problems 390 390 License Not Available **Floating License Server Communication Timeout** 390 Translating Configuration Files from Other Logic Analyzers 392 To translate 167xG logic analyzer configuration files 392 To translate 16700-series logic analyzer configuration files 393 395 **Running Self Tests** 397 Accessing Japanese Online Help 400 If there are problems writing CDs on a 16900A, 16902A, or 16903A frame **Hibernation Is Not Supported** 401 402 Network Troubleshooting Guide Remote Desktop Set Up 405 For More Information 406 Intrinsic Support 408

#### **11 Concepts**

When should you use an oscilloscope?410When should you use a logic analyzer?411

```

What is a logic analyzer?

412

Sampling clock in the timing analyzer

412

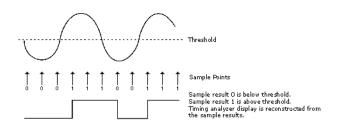

Sampling in the timing acquisition mode

413

Triggering the timing analyzer

414

Sampling clock in the state analyzer

415

Sampling in the state acquisition mode

415

416

Triggering the state analyzer

Pod and Channel Naming Conventions

418

Why Are Pods Missing?

419

Memory Depth and Channel Count Trade-offs

420

Transitional Timing

422

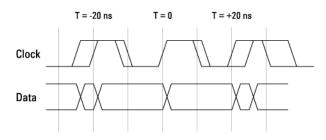

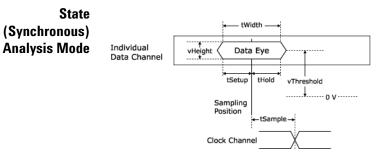

Understanding State Mode Sampling Positions

424

Eye Scan in Logic Analyzers that Support Differential Signals

428

Understanding Logic Analyzer Triggering

431

The Conveyor Belt Analogy

431

Summary of Triggering Capabilities

432

Sequence Steps

433

Boolean Expressions

435

Branches

436

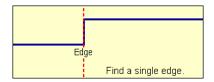

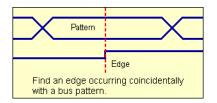

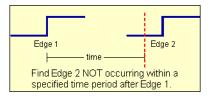

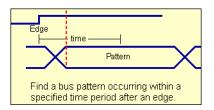

Edges

436

437

Ranges

437

Flags

Occurrence Counters and Global Counters

437

438

Timers

Storage Qualification

439

Strategies for Setting Up Triggers

440

Conclusions

444

ALA vs. XML, When to Use Each Format

445

Multiframe Logic Analysis Systems

446

Agilent Logic Analyzer vs. 16700 Terminology

449

```

#### **12 Reference**

```

Menus

453

File Menu

453

Edit Menu

454

View Menu

456

Setup Menu

456

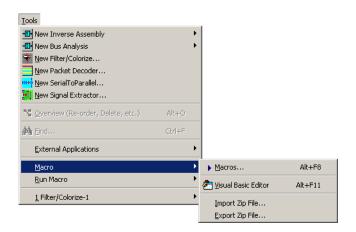

Tools Menu

458

Markers Menu

460

461

Run/Stop Menu

Overview Menu

462

462

Listing Menu

Waveform Menu

462

Compare Menu

463

Source Menu

464

Protocol Viewer Menu

464

VbaView Menu

465

Window Menu

466

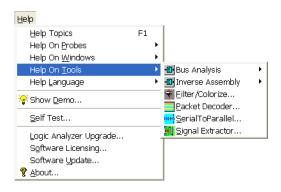

Help Menu

467

Toolbars

469

Standard Toolbar

469

Pattern Generator Toolbar

470

Analyzer Setup Toolbar

471

External Oscilloscope Setup Toolbar

471

Data Import Toolbar

472

Probes Toolbar

472

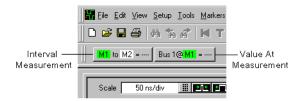

Markers Toolbar

472

Run/Stop Toolbar

473

Visual Basic Toolbar

473

To customize toolbars

474

Marker Measurement Display Bar

475

Windows

476

Waveform Display Window

476

482

Listing Display Window

Compare Display Window

485

Source Display Window

486

Protocol Viewer Display Window

487

VbaView Window

490

Overview Window

491

```

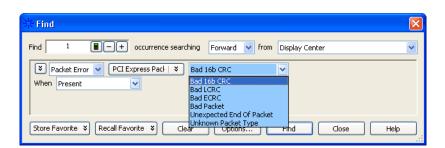

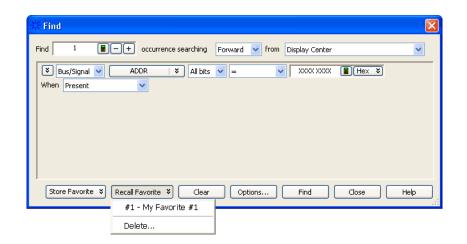

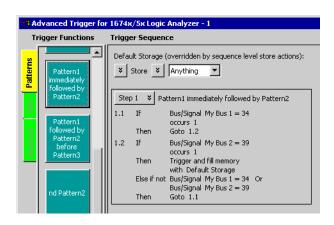

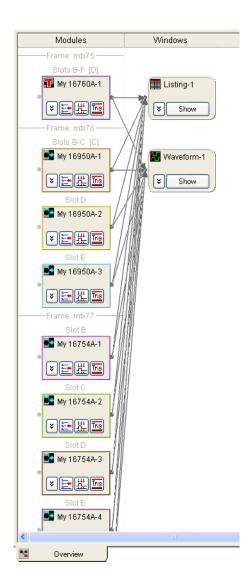

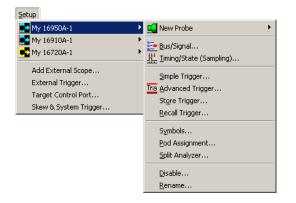

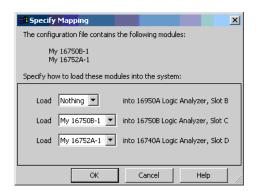

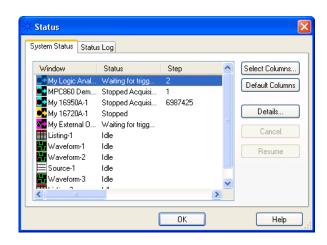

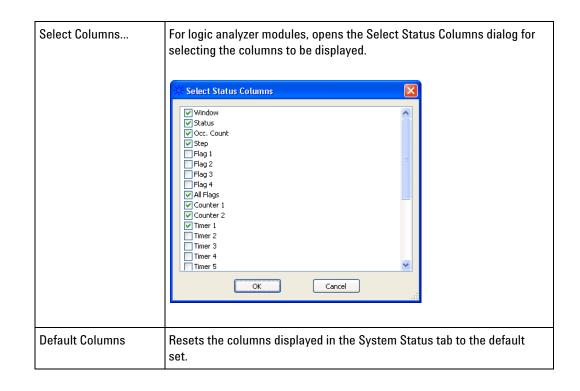

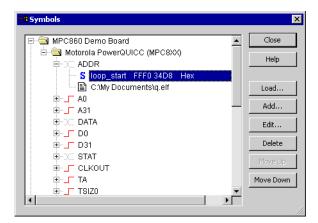

494 Dialogs Advanced Clocking Setup Dialog 495 Advanced Trigger Dialog 496 Agilent Logic Analyzer Upgrade Dialog 497 Analyzer Setup Dialog 498 **Chat Dialog** 501 Chat Select Destination Dialog 502 **Choose a Protocol Family and Bus Dialog** 502 **Create a New Configuration Dialog** 503 E-mail Dialog 504 **Event Editor Dialog** 505 **Export Dialog** 506 **Export File Selection Dialog** 507 508 External Application Setup Dialog External Trigger Dialog 510 **Find Dialog** 511 Frame/Module Information Dialog 513 Import Dialog 514 Import Setup Dialog 515 Module Mapping Dialog 517 Module Skew and System Trigger Dialog 520 Netlist Import Dialog 520 **Offline Startup Options Dialog** 521 **Options Dialog** 522 Pod Assignment Dialog 524 Printing Data Dialog 525 **Properties Dialog** 526 **Range Properties Dialog** 526 **Recall Trigger Dialog** 527 **Run Properties Dialog** 529 Select Symbol Dialog 530 Select System to Use Dialog 531 Software Licensing Dialog 534 Source Viewer Properties Dialog 538 Specify Mapping Dialog 540 Split Analyzer Setup Dialog 541 Status Dialog 542 Symbols Dialog 545 System Summary Dialog 546 **Target Control Port Dialog** 549 **Thresholds and Sample Positions Dialog** 550

```

TimingZoom Setup Dialog

558

Trigger Functions

560

Timing Mode Trigger Functions

560

State Mode Trigger Functions

573

Data Formats

588

ALA Format

588

Standard CSV Format

588

Module CSV Format

589

Module Binary (ALB) Format

598

Object File Formats Supported by the Symbol Reader

600

General-Purpose ASCII (GPA) Symbol File Format

601

General-Purpose ASCII (GPA) Record Format Summary

602

SECTIONS

603

FUNCTIONS

604

USER

604

VARIABLES

605

SOURCE LINES

606

START ADDRESS

606

Comments

606

Product Overviews

608

1680/1690-Series Logic Analyzer Product Overview

608

16800-Series Logic Analyzer Product Overview

614

16900-Series Logic Analysis System Product Overview

617

U4154A Logic Analyzer Product Overview

626

16850-Series Logic Analyzer Product Overview

628

Agilent Logic and Protocol Analyzer Application Product Overview

631

Logic Analyzer Notes

635

637

1680/1690-Series Logic Analyzer Notes

16740/41/42 Logic Analyzer Notes

638

16750/51/52 Logic Analyzer Notes

640

16753/54/55/56 Logic Analyzer Notes

643

16760 Logic Analyzer Notes

645

16800-Series Logic Analyzer Notes

651

654

16910/11 Logic Analyzer Notes

656

16950/51 Logic Analyzer Notes

16960 Logic Analyzer Notes

658

16962 Logic Analyzer Notes

668

U4154A Logic Analyzer Notes

676

16850-Series Logic Analyzer Notes

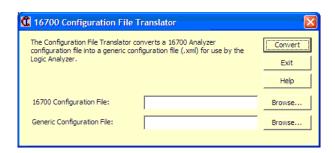

711

```

Specifications and Characteristics 714

1680/1690-Series Logic Analyzer Specifications and Characteristics 714 16740/41/42 Logic Analyzer Specifications and Characteristics 717 16750/51/52 Logic Analyzer Specifications and Characteristics 722 16753/54/55/56 Logic Analyzer Specifications and Characteristics 727 16760 Logic Analyzer Specifications and Characteristics 734 16800-Series Logic Analyzer Specifications and Characteristics 742 16910/11 Logic Analyzer Specifications and Characteristics 749 16950/51 Logic Analyzer Specifications and Characteristics 757 764 16960 Logic Analyzer Specifications and Characteristics 16962 Logic Analyzer Specifications and Characteristics 769 16900-Series Logic Analysis System Frame Characteristics 774 U4154A Logic Analyzer Specifications and Characteristics 775 779 16850-Series Logic Analyzer Specifications and Characteristics What is a Specification? 785 What is a Characteristic? 786

#### **13 Glossary**

Index

Agilent Logic and Protocol Analyzer Online Help

# What's New

In this release, version 05.80, of the Agilent Logic and Protocol Analyzer application, the following changes have been made:

- U4431A MIPI M-PHY Analyzer module The Agilent Logic and Protocol Analyzer application now adds support for a new AXIe-based module introduced with this release to capture and decode M-PHY, UniPro, UFS, SSIC, and CSI-3 data. This module is installed in an Agilent AXIe chassis and configured and controlled using the Agilent Logic and Protocol Analyzer application. Refer to the U4431 M-PHY Analyzer Online Help to know how to configure and use with module.

- U4301 PCIe Gen3 analyzer module -

- You can now decode AHCI transactions as well in addition to NVMe and PCIe transactions from the data captured by the U4301 module. Refer to the topic *Computing and Viewing Decoded Transactions* in the U4301 PCIe Gen3 Analyzer Online Help for more information.

- A new feature, *Flow Control* is now available in the PCIe Performance Overview tab of the Protocol Viewer. This feature allows you to compute and track the available flow control credits for the data trace that has bidirectional PCIe traffic. Refer to the topic *Viewing Offline Performance Summary* in the U4301 PCIe Gen3 Analyzer Online Help for more information.

- DDR/LPDDR tools enhancements -

- A new tool named *DDR/LPDDR Custom Configuration Creator* has been added to the *Agilent DDR Setup Assistant and Eyefinder* software package. This tool allows you to define the footprints layout as per your custom probing solution used in the DDR/LPDDR setup and then create an XML configuration file based on this footprint information. Refer to the tool's online help to know more. The online help is accessible from the tool's GUI and also installed at <*logic and protocol analyzer install location*> \*help*\.

- The *B4623 LPDDR Decoder* now supports decoding and displaying the entry to and exit from Self Refresh and Power Down events. Refer to the topic *Decoding Self Refresh and Power Down Events* in the *LPDDR Bus Decoder Online Help*.

- Five new LPDDR2/3 tests have been added to the DDR Post Process Compliance tool to handle compliance parameters related to power down and self refresh modes. Three of these tests have also been added to the Real Time Compliance tool.

- Support for DDR4 running at > 2.5GHz added.

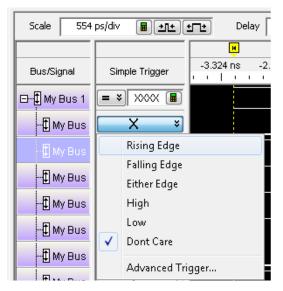

- **Trigger on edge** For 16850-series and U4154A logic analyzer modules, you can now set a trigger on Rising, Falling, or Either edge in the Timing Asynchronous sampling mode as well as State –Synchronous sampling mode. Refer to the topics *Specifying Simple Triggers* and *Specifying Advanced Triggers* in the *Logic and Protocol Analyzer* online help.

#### See Also • "Version 05.70 What's New" on page 21

- "Version 05.60 What's New" on page 23

- "Version 05.50 What's New" on page 25

- "Version 05.40 What's New" on page 27

- "Version 05.30 What's New" on page 29

- "Version 05.20 What's New" on page 31

- "Version 05.00 What's New" on page 34

- "Version 04.00 What's New" on page 36

- "Version 03.83 What's New" on page 37

- "Version 03.82 What's New" on page 39

- "Version 03.80 What's New" on page 40

- "Version 03.70 What's New" on page 41

- "Version 03.67 What's New" on page 43

- "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 05.70 What's New

In this release, version 05.70, of the Agilent Logic and Protocol Analyzer application, the following changes have been made:

- **16850 series portable logic analyzers** With this release, the Agilent Logic and Protocol Analyzer application can also be installed and used with the newly introduced 16850 series portable logic analyzers. Refer to the topic *16850-Series Logic Analyzer Notes* to know more about this new series of logic analyzers.

- **Transaction decoding** You can now compute and view decoded transactions from the captured PCIe data using the newly added Transaction Decode tab in the Protocol Viewer. Currently, the support for decoding NVMe transactions is added. The transaction decoding feature is a licensed option. Refer to the help book *Viewing Decoded Transactions* in the U4301 PCIe Gen3 Analyzer online help to know more.

- Offline performance summary computation You can now compute and view offline performance summary from the captured PCIe data using the newly added PCIe Performance Overview tab in the Protocol Viewer. This tab presents statistics for various performance parameters in tabular as well as charts form. The offline performance summary feature is a licensed option. Refer to the help book *Viewing Offline Performance Summary* in the U4301 PCIe Gen3 Analyzer online help to know more.

#### See Also • "Version 05.60 What's New" on page 23

- "Version 05.50 What's New" on page 25

- "Version 05.40 What's New" on page 27

- "Version 05.30 What's New" on page 29

- "Version 05.20 What's New" on page 31

- "Version 05.00 What's New" on page 34

- "Version 04.00 What's New" on page 36

- "Version 03.83 What's New" on page 37

- "Version 03.82 What's New" on page 39

- "Version 03.80 What's New" on page 40

- "Version 03.70 What's New" on page 41

- "Version 03.67 What's New" on page 43

- "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 05.60 What's New

In this release, version 05.60, of the Agilent Logic and Protocol Analyzer application, the following changes have been made:

- Windows 8 and Windows Server 2008 support added With this release, you can install the Agilent Logic and Protocol Analyzer application on a host with Windows 8 or Windows Server 2008 operating system.

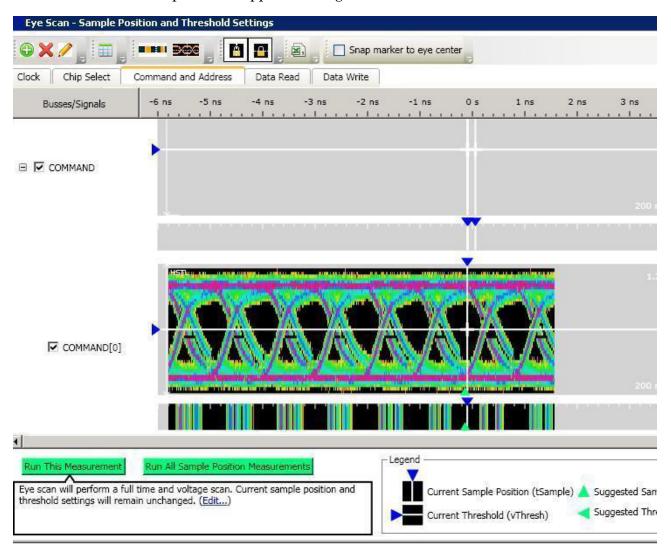

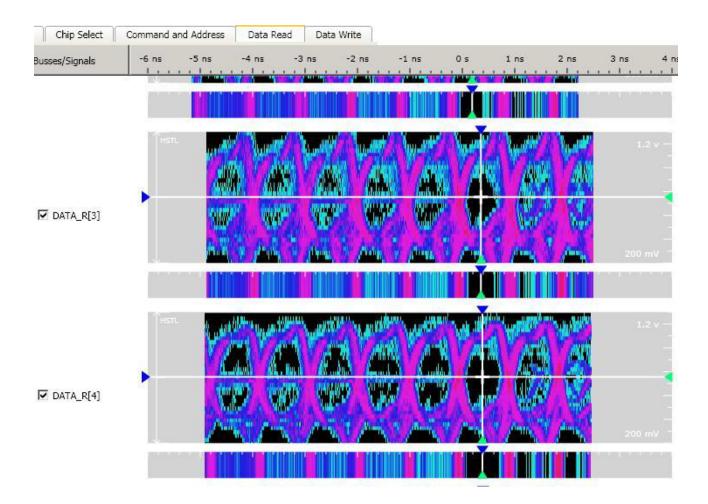

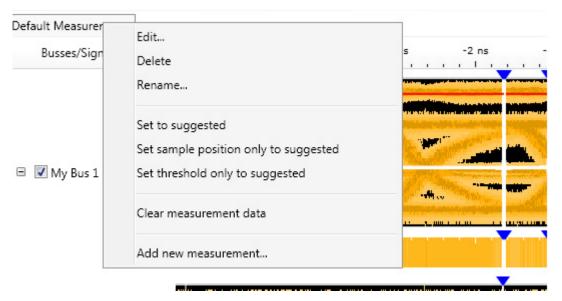

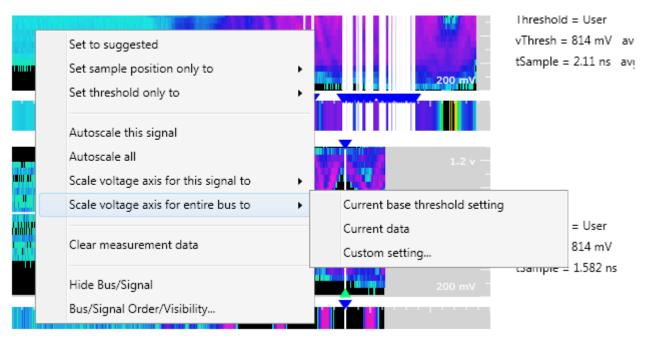

- Enhancements have been made to the Eyescan feature The eyescan feature now supports scaling the voltage axis for an entire bus to a selected value in an eyescan diagram. To know more, refer to the topic "Setting up and Running Eyescans in U4154A Logic Analyzer" on page 690.

- **B462X software packages** Both A and B versions of the licenses for B4621/2/3 software packages are now supported in the Logic and Protocol Analyzer application. B version is an upgrade to A version and therefore provides additional capabilities and features. To know more about the feature difference, refer to the *Online help* of these software packages.

- **Repetitive run feature in the DDR Post Process Compliance tool** -You can now run the selected tests in a repetitive mode. To accomplish this, the tool runs the logic analyzer repetitively for data acquisition and then run the tests repetitively on the newly acquired data. To know more, refer to the *DDR Post Process Compliance Tool Online Help*.

- **BMC Firmware Upgrade utility** A new utility named BMC Firmware Upgrade has been provided. This utility upgrades the BMC firmware of a module to the latest version provided with the Logic and Protocol Analyzer software. To know more, refer to the *Agilent AXIe Based Logic Analysis and Protocol Test Module Installation Guide*.

- Support for five independent modules in a chassis You can now install and use five independent modules in an Agilent five-slot AXIe chassis. In earlier releases, a maximum of three module sets were supported. (A module set can be either a single module or a group of modules cabled together to operate as a module.)

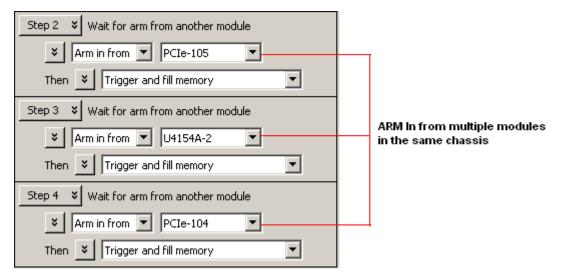

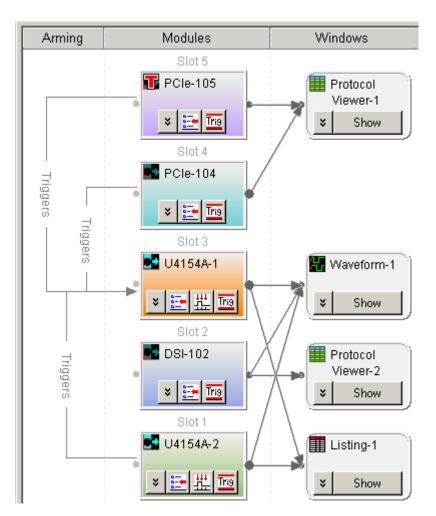

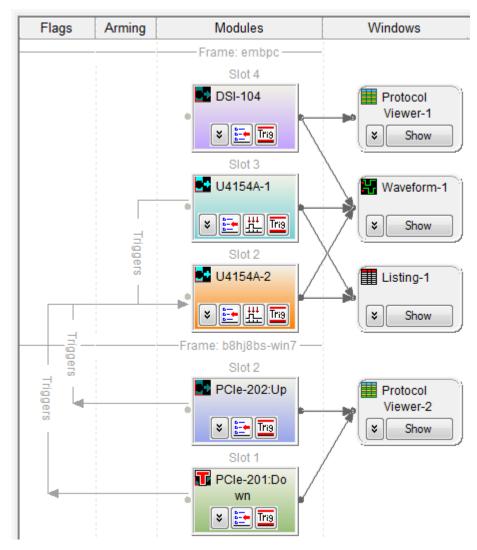

- "Or-ing" ARM In support added in triggering You can now set the trigger configurations of an AXIe based module to ARM In from multiple modules in the same chassis or another connected chassis/ logic analysis frame (in a multiframe setup). An AXIe module can now receive ARM IN signals from an "OR'ed" combination of trigger out signals from multiple modules. Refer to the topic "To arm one module with another module's trigger" on page 193 to know more.

- See Also "Version 05.50 What's New" on page 25

- "Version 05.40 What's New" on page 27

- "Version 05.30 What's New" on page 29

- "Version 05.20 What's New" on page 31

- "Version 05.00 What's New" on page 34

- "Version 04.00 What's New" on page 36

- "Version 03.83 What's New" on page 37

- "Version 03.82 What's New" on page 39

- "Version 03.80 What's New" on page 40

- "Version 03.70 What's New" on page 41

- "Version 03.67 What's New" on page 43

- "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 05.50 What's New

In this release, version 05.50, of the Agilent Logic and Protocol Analyzer application, the following changes have been made:

- U4421A MIPI D-PHY Analyzer and Exerciser module The Agilent Logic and Protocol Analyzer application now adds support for a new module introduced with this release to send D-PHY stimulus and capture and decode D-PHY data. This module is installed in Agilent AXIe chassis and configured and controlled using the Agilent Logic and Protocol Analyzer application. Refer to the U4421 D-PHY Analyzer and Exerciser Online Help to know how to configure and use with module.

- U4301A PCIe Gen3 Analyzer module You can now use the Agilent Logic and Protocol Analyzer application to create a physical layer tuning (.ptu) file for tuning the U4301A analyzer for a DUT. The creation and fine tuning of a ptu file is now GUI based. For more information, refer to the topic *Tuning the Analyzer for a Specific DUT* in the U4301A PCIe Gen3 Analyzer Online Help.

- USB connectivity between AXIe chassis and host computer You can now connect the host computer to the AXIe chassis via PCIe or USB. The USB connectivity support has been added as a licensed option. Refer to the AXIe based Logic Analysis & Protocol Test Modules Installation Guide to know more.

- **B4621B, B4622B, and B4623B software packages** These packages replace the B4621A, B4622A, and B4623A software packages and have the following new additions/updates -

- B4621B Decoder support for DDR4 added.

- B4623B Decoder support for LPDDR3 added.

- B4622B -

- The three tools contained in this toolset now support DDR, DDR2, DDR3, DDR4, LPDDR, LPDDR2, and LPDDR3. Several new tests have been added for DDR3/4 and LPDDR2/3.

- A new tool *Real-Time Compliance Tool* has been added that evaluates DDR/LPDDR data in real- time to detect and report violations to compliance limits specified in DDR/LPDDR specifications. Refer to the *Real-Time Compliance Tool Online Help* to know more.

- The DDR Validation Tool has been renamed to DDR Post Process Compliance Tool.

• DDR Setup Assistant and DDR Eyescan have been enhanced to include support for LPDDR3 and DDR4. These have also been updated to handle finding the chip select eyes in a separate measurement from the clock. Refer to the DDR Setup Assistant online help and Modifying General or Target-specific Scan Qualifications in this user guide to know more.

#### See Also • "Version 05.40 What's New" on page 27

- "Version 05.30 What's New" on page 29

- "Version 05.20 What's New" on page 31

- "Version 05.00 What's New" on page 34

- "Version 04.00 What's New" on page 36

- "Version 03.83 What's New" on page 37

- "Version 03.82 What's New" on page 39

- "Version 03.80 What's New" on page 40

- "Version 03.70 What's New" on page 41

- "Version 03.67 What's New" on page 43

- "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 05.40 What's New

In this release, version 05.40, of the Agilent Logic and Protocol Analyzer application, the following changes have been made:

- U4301A PCIe Gen3 Analyzer module

- LTSSM Overview pane added in the Protocol Viewer window You can now view the LTSSM states and their transitions for the PCIe data that you captured using the U4301 module. A new pane called LTSSM Overview has been introduced in the Protocol Viewer window to display these states and transitions. To know about this feature, refer to the topic *Viewing LTSSM States and Transitions* in the U4301 PCIe Gen3 Analyzer Online Help.

- U4154A Logic Analyzer module

- Eyescan enhancements The eyescan feature of the U4154A module has been enhanced to allow you to modify the general as well as DDR-specific scan qualification. To know about these enhancements, refer to the topic *Modifying General or Target-specific Scan Qualification* in this Online Help.

#### See Also

- "Version 05.30 What's New" on page 29

- "Version 05.20 What's New" on page 31

- "Version 05.00 What's New" on page 34

- "Version 04.00 What's New" on page 36

- "Version 03.83 What's New" on page 37

- "Version 03.82 What's New" on page 39

- "Version 03.80 What's New" on page 40

- "Version 03.70 What's New" on page 41

- "Version 03.67 What's New" on page 43

- "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 05.30 What's New

In this release, version 05.30, of the Agilent Logic Analyzer application, the following changes have been made:

- U4301A PCIe Gen3 Analyzer module

- x8 bidirectional configurations supported on a single U4301A module – With this release, a single U4301A module can support a bidirectional (upto x8) configuration. You can use the same U4301A module to probe and capture data in both upstream as well as downstream directions. For detailed information on how to use the U4301A module in bidirectional configurations, refer to the PCI Express Gen3 Hardware and Probing Guide. This guide is available on www.agilent.com and also installed with the Logic Analyzer software at <Logic Analyzer Install location>\help\pdfs.

- U4324A PCIe Gen3 Flying Lead probe support added Besides the existing probing options, you can now use the new U4324A flying lead probes with the U4301A Analyzer module. For detailed information on this probe and its setup, refer to the PCI Express Gen3 Hardware and Probing Guide. This guide is available on www.agilent.com and also installed with the Logic Analyzer software at <Logic Analyzer Install location>\help\pdfs.

- U4154A Logic Analyzer module

- A new license option 01G has been introduced for the U4154A module. You now have two license options, 01G and 02G available for the U4154A module. Based on the license option that you purchase, the state speed for the U4154A module is set. A "01G" license sets maximum state speed of U4154A to 1.4Gbs. A "02G option sets it to 2.5Gbs. These license options do not however control and set the timing speed of the module. Besides setting the state speed to 2.5Gbs, the 02G option also provides High Resolution (4.8 ps of time resolution) in eyescans which is not available with the 01G option.

- **Eyescan enhancements** The eyescan feature of the U4154A module has been enhanced to allow you to modify the unit interval settings, adjusting the sample position markers, enabling/disabling the marker placements to the center of the eye and setting sample positions to their suggested sample positions in a single click. To know about these enhancements, refer to the topic "Setting up and Running Eyescans in U4154A Logic Analyzer" on page 690 in this user guide.

- U4998A HDMI Protocol/Audio/Video Analyzer and Generator module

- **MHL testing support added** Besides supporting HDMI 1.4a and 1.4b, the module now supports the MHL protocol as well. You can now use this module to test MHL source and sink DUTs as well. To know more, refer to the U4998A HDMI and MHL Protocol/Audio/Video Analyzer and Generator Online Help.

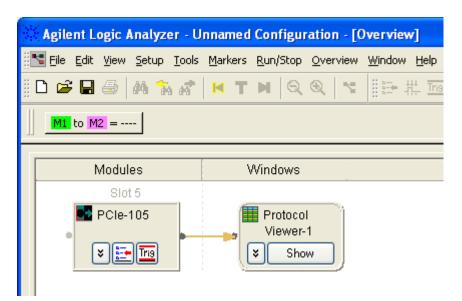

- The Protocol Viewer window has replaced the legacy Packet Viewer window. You can now use Protocol Viewer to display the data captured by the U4301A PCIe Gen3 Analyzer module. To know more about Protocol Viewer, refer to the topic Protocol Viewer Window in this user guide.

- See Also "Version 05.20 What's New" on page 31

- "Version 05.00 What's New" on page 34

- "Version 04.00 What's New" on page 36

- "Version 03.83 What's New" on page 37

- "Version 03.82 What's New" on page 39

- "Version 03.80 What's New" on page 40

- "Version 03.70 What's New" on page 41

- "Version 03.67 What's New" on page 43

- "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 05.20 What's New

In this release, version 05.20, of the Agilent Logic Analyzer application:

- You can now use the Agilent AXIe M9536A Embedded Controller module as the host computer with the AXIe based instrument modules installed in AXIe chassis. The instrument modules that support this controller module include U4998A HDMI Analyzer, U4301A PCIe Gen3 Analyzer, and U4154A Logic Analyzer modules. The Embedded Controller module is a one-slot module that needs to be installed in slot 1 of the AXIe chassis.

- Windows 7 support has been added for the 16800 and 16900 series of Logic Analyzers with serial number MY51420101 or higher. With the 05.20.0000 release of the Agilent Logic Analyzer application, 16800-series logic analyzers and 16900-series logic analysis systems are shipped from the factory with Windows 7 operating system. Refer to the 16800 and 16900 Install guides to know about the Windows 7 specific procedures, firewall settings and the new recovery procedure of 16800 and 16900 series of Logic Analyzers for Windows 7. These guides are installed with the Logic Analyzer software at <Logic Analyzer Install location>\help\pdfs.

- U4301 PCIe Analyzer module The following changes have been made to the U4301A PCIe Gen3 Analyzer module.

- The Protocol Viewer window now has an additional tab Traffic Overview" in its lower pane. This tab displays the traffic statistics for the captured PCIe packets displayed in the upper pane of Protocol Viewer. It displays the count of captured packets based on packet types and the link direction (upstream or downstream). Refer to the topic Viewing PCIe Gen3 Packets in the U4301 PCIe Gen3 Analyzer online help to know more.

- A new feature "CSV Export" has been added to the Protocol Viewer window. This feature allows you to export the displayed PCIe packet data from Protocol Viewer to a specified .csv file. Refer to the topic "Viewing PCIe Gen3 Packets" in the U4301 PCIe Gen3 Analyzer online help to know more.

- U4154A Logic Analyzer module The following changes have been made to the U4154A module features.

- A new license option 01G has been introduced for the U4154A module. You now have two license options, 01G and 02G available for the U4154A module. Based on the license option that you purchase, the state speed for the U4154A module is set. A "01G" license sets maximum state speed of U4154A to 1.4Gbs. A "02G option sets it to 2.5Gbs. These license options do not however control and set the timing speed of the module. Besides setting the state speed to 2.5Gbs, the 02G option also provides High Resolution (4.8 ps of time resolution) in eyescans which is not available with the 01G option.

- The eyescans that you set up and run using the U4154A module now include a scan resolution selection feature. If you have the 02G license of the U4154A module, you can either choose a Normal or a High resolution for eyescans. To know more, refer to the topic "Setting up and Running Eyescans in U4154A Logic Analyzer" on page 690 to know more about the eyescan resolutions.

- You can now export eyescan data from the Eye Scan Sample Position and Threshold Settings dialog box to a specified .csv file. To know more, refer to the topic "Setting up and Running Eyescans in U4154A Logic Analyzer" on page 690.

- The Transitional / Store Qualified Half Channel 5.0 GHz mode is now available as a Timing mode sampling option for the U4154A module. For details on this mode, refer to "U4154A Logic Analyzer Notes" on page 676.

- See Also "Version 05.00 What's New" on page 34

- "Version 04.00 What's New" on page 36

- "Version 03.83 What's New" on page 37

- "Version 03.82 What's New" on page 39

- "Version 03.80 What's New" on page 40

- "Version 03.70 What's New" on page 41

- "Version 03.67 What's New" on page 43

- "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 05.00 What's New

In this release, version 05.00, of the Agilent Logic Analyzer application:

- You can now use the Agilent Logic Analyzer application with the new U4154A Logic Analyzer module hosted in the new Agilent AXIe chassis (for example the M9502A portable 2-slot chassis). U4154A is a 136 channel AXIe based high speed state and timing logic analyzer.

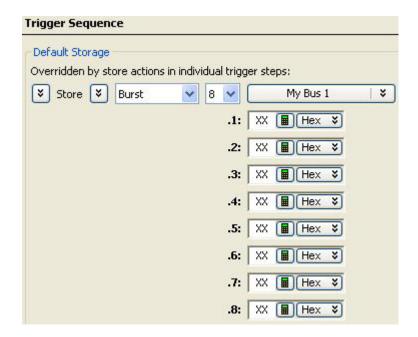

- Trigger capabilities have been enhanced with more levels and deeper bursts (burst levels increased from 4 to 8). New event counter added for specifying the trigger action.

- 12.5 GHz Timing zoom support added for the U4154A Logic Analyzer module. The support has been added for state as well as timing sampling modes.

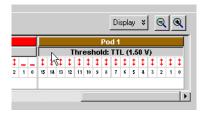

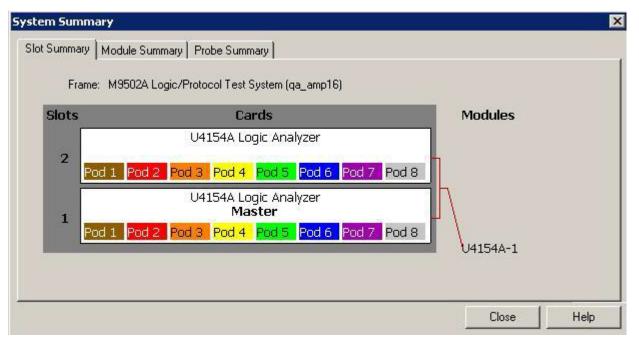

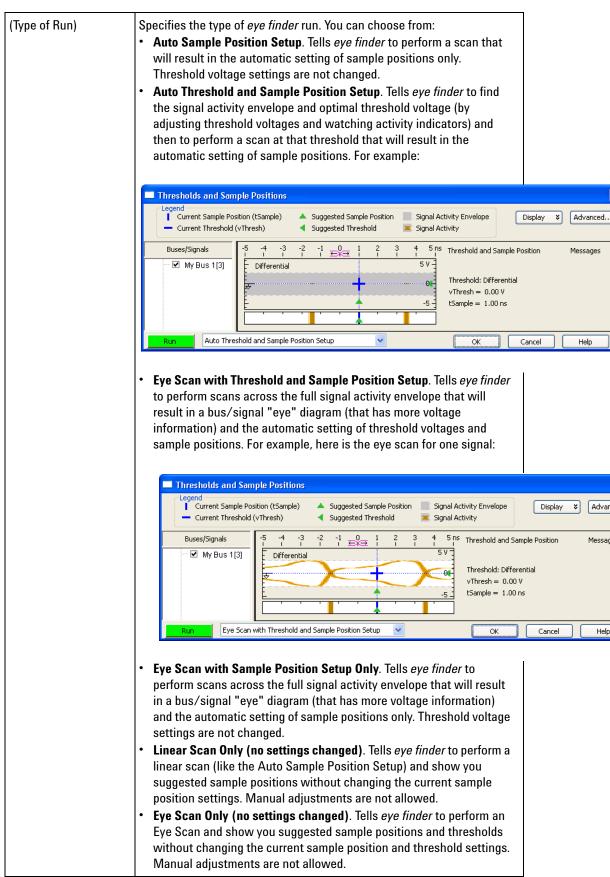

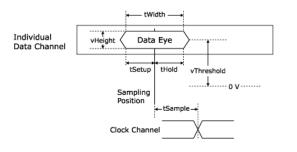

- The eye scan feature has been added for U4154A to determine optimal threshold voltage and sample position settings for individual channels and automatic adjustment of these settings. Eye scan triggers added to add trigger conditions for the samples that U4154A takes during the eye scan.

- One state clock provided to generate state clock signals for the U4154A logic analyzer module. Four state clock qualifiers have been added to allow you to add conditions to the state clock using qualifiers.

- The Force Prestore option added in the sampling trigger position.

- Advanced probe settings enabled for U4154A and 16962 logic analyzers. You can enable or disable the peaking at the channel/pod/module level for the probing system used for these logic analyzers.

- Two full channel modes (Full channel at 2.5 GHz and Transitional / Store qualified Full channel at 2.5 GHz) and one half channel mode at 5.0 GHz supported for U4154A. Quarter channel timing mode and Transitional / Store qualified Half channel mode not available for the U4154A Logic Analyzer module.

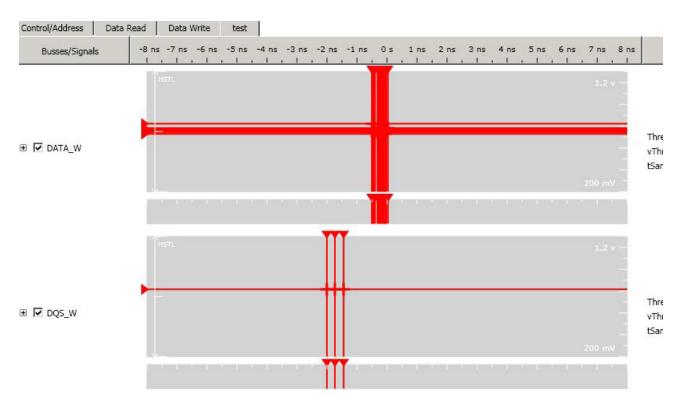

- DDR Setup Assistant tool enhanced to support the set up of the U4154A Logic Analyzer using this tool with automated steps for determining and setting up the sample positions for command, address, and data read and write signals.

- Support for Agilent U4998A HDMI Protocol/Audio/Video capture and generate (PAG) module added. You can now use the Agilent Logic Analyzer application with this module hosted in the Agilent AXIe or AMP chassis.

- Data storage qualifiers, ASPM (power management) support, and lane viewer added in the U4301A PCIe 8 Gbps protocol analyzer.

- See Also "Version 04.00 What's New" on page 36

- "Version 03.83 What's New" on page 37

- "Version 03.82 What's New" on page 39

- "Version 03.80 What's New" on page 40

- "Version 03.70 What's New" on page 41

- "Version 03.67 What's New" on page 43

- "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 04.00 What's New

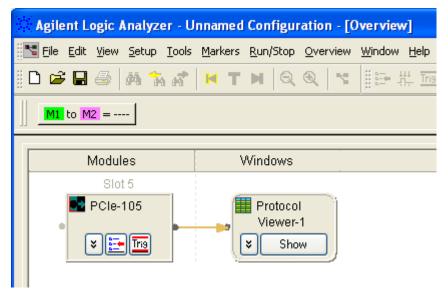

- The *Agilent Logic Analyzer* application adds support for the new Agilent Digital Test Console chassis (for example the U4002A portable 2-slot chassis) and the U4301 PCIe Gen3 analyzer blade. See "U4301 PCIe Gen3 Analyzer—At a Glance" (in the online help).

- The DDR Setup Assistant has been added. The DDR Setup Assistant helps you properly set up a logic analysis system given the type of logic analyzer, DDR bus, and probing solution. Many of the set up steps are now automated. See "DDR Setup Assistant—At a Glance" (in the online help).

- The "LPDDR Bus Decoder" (in the online help) software is now available; it lets you view transactions, commands, and data captured on LPDDR buses.

#### See Also • "Version 03.83 What's New" on page 37

- "Version 03.82 What's New" on page 39

- "Version 03.80 What's New" on page 40

- "Version 03.70 What's New" on page 41

- "Version 03.67 What's New" on page 43

- "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 03.83 What's New

In version 03.83, of the Agilent Logic Analyzer application:

- Colorized DDR2/DDR3 eye scan measurements, using the 16962A logic analyzer module, were added. These measurements provide new DDR measurement capabilities:

- Place sample points far more accurately than ever before to get the most reliable data capture.

- View event qualified eye diagrams to assess both functional and parametric behavior of the device under test. With this new capability, you can rapidly view eye characteristics and identify design defects like inter-symbol interference and driver contention.

- Gain signal integrity insight and identify problem signals quickly by simultaneously scanning all of the signals in your system.

- The N4851B MIPI D-PHY acquisition probe and N4861B MIPI D-PHY stimulus probe were supported. Also, the capabilities of existing N4851A and N4861A MIPI D-PHY probes are enhanced (as described below with the purchase of the N4851U-004).

MIPI D-PHY analysis additions:

- 3 and 4 lane analysis support at up to 940 Mb/s for the N4851B.

- 3 and 4 lane analysis support at up to 800 Mb/s for the N4851A (requires purchase of the N4851U-004 to access this capability).

Stimulus capabilities:

- 3 lane stimulus support at up to 1 Gb/s for the N4861B.

- 3 lane stimulus support at up to 500 Mb/s for the N4861A (requires purchase of the N4851U-004 to access this capability).

For more information, see "N4851A/B, N4861A/B MIPI D-PHY Acquisition/Stimulus Probes" (in the online help).

- The Add External Oscilloscope wizard was updated to support the latest Agilent oscilloscopes. For the complete list of supported oscilloscopes, see "External Oscilloscope Time Correlation and Data Display" (in the online help).

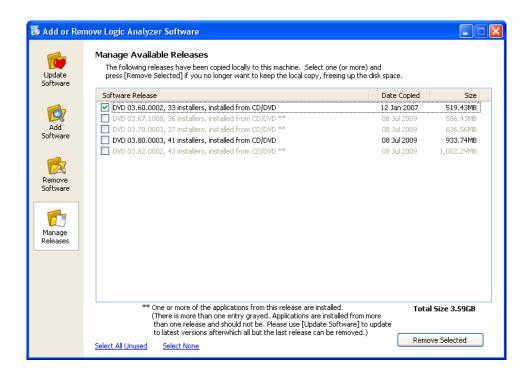

- The Add or Remove Agilent Logic Analyzer Software tool was updated to let you manage releases, that is, to let you remove old releases and free disk space. See Chapter 9, "Updating Software," starting on page 367.

- See Also "Version 03.82 What's New" on page 39

- "Version 03.80 What's New" on page 40

- "Version 03.70 What's New" on page 41

- "Version 03.67 What's New" on page 43

- "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 03.82 What's New

In version 03.82, of the Agilent Logic Analyzer application:

- The new 16962A logic analyzer card was supported in the 16900-series logic analysis system. See "16962 Logic Analyzer Notes" on page 668.

- See Also "Version 03.80 What's New" on page 40

- "Version 03.70 What's New" on page 41

- "Version 03.67 What's New" on page 43

- "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 03.80 What's New

In version 03.80 of the Agilent Logic Analyzer application:

- Timing analysis modes and additional triggering capabilities were added to the 16960A logic analyzer. See "16960 Logic Analyzer Notes" on page 658.

- The *Agilent Logic Analyzer* application supported the Windows<sup>®</sup> Vista operating system in addition to the Windows<sup>®</sup> XP operating system.

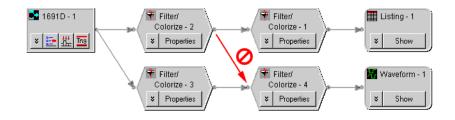

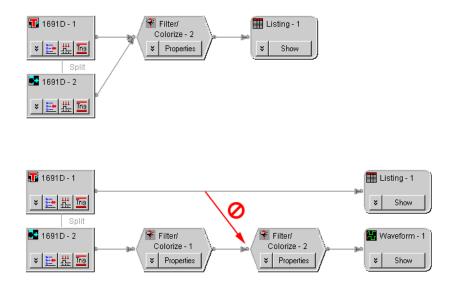

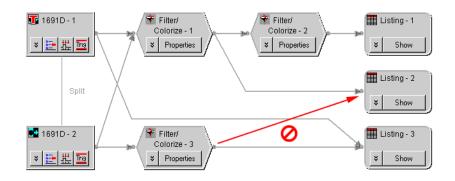

- An option in the Filter/Colorize tool to specify how the operation is applied across multiple data sources was added. See "To change the "across all data" option" (in the online help).

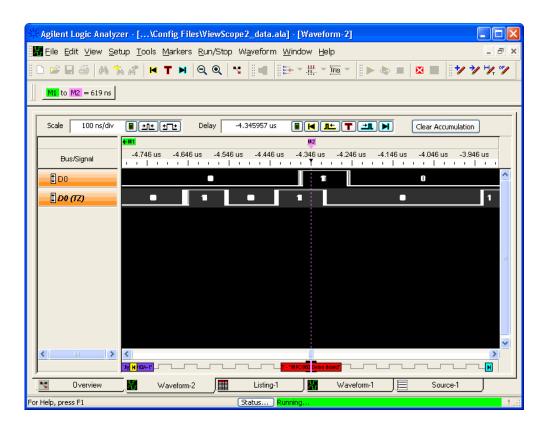

- An option to accumulate waveforms in the Waveform window was added. See "To accumulate waveforms" on page 252.

- There were additions to the Signal Extractor tool to allow it to convert timing analysis captures of serial buses into samples that can be decoded and displayed using the Packet Decoder and Packet Viewer. See "What's New in the Signal Extractor Tool" (in the online help).

See Also • "Version 03.70 What's New" on page 41

- "Version 03.67 What's New" on page 43

- "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 03.70 What's New

In version 03.70 of the Agilent Logic Analyzer application:

- Support for the new 16902B logic analysis system was added. See 16900-Series Logic Analysis System Product (see page 617).

- The N4850A DigRF v3 acquisition probe for decoding and displaying DigRF v3 signals and the N4860A DigRF v3 stimulus probe for generating digital signals to emulate baseband IC or RF IC signals was supported. See "N4850/60A DigRF v3 Acquisition/Stimulus Probes" (in the online help).

- The Run Properties dialog that lets you save captured data after each run and stop after a certain number of repetitive runs was added. See Run Properties Dialog (see page 529).

- The Protocol Development Kit (PDK) editor added intelligent context-sensitive popup menus that show valid XML elements and attributes at the cursor location. These popup menus make editing protocol definition files easier. There have also been some minor improvements to the protocol description file XML elements and attributes, the Packet Decoder tool, and the Packet Viewer window. See "Protocol Development Kit (PDK)" (in the online help).

- The COM Connection Tool for testing the COM Automation connection between a controller PC and a logic analysis system was added. See "Test your Distributed COM connection" (in the online help).

- The "Signal Extractor" (in the online help) tool was enhanced with new commands and debugging features to help extract data from one input bus/signal and place it on multiple output buses/signals.

- The *Agilent Logic Analyzer* application required the Windows<sup>®</sup> XP operating system and no longer supported the Windows 2000 operating systems.

**See Also** • "Version 03.67 What's New" on page 43

- "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 03.67 What's New

In version 03.67 of the Agilent Logic Analyzer application:

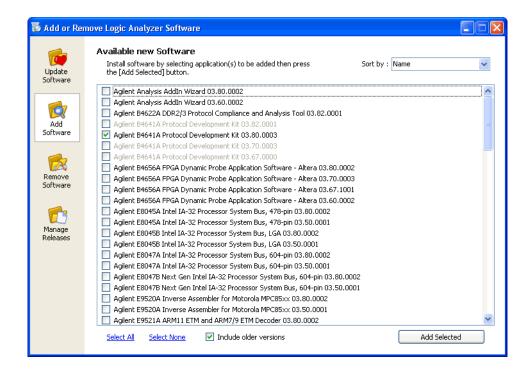

- The Add or Remove Agilent Logic Analyzer Software tool was added to help you manage your logic analyzer software and keep it up to date. See Updating Software (see page 367).

- The "FPGA Dynamic Probe for Xilinx FPGAs" (in the online help) supported connecting to JTAG cables on remote PCs or logic analysis systems.

- The pattern generator was enhanced to: let you find instructions or vectors in the sequence, let you use macro, loop, and comment instructions when importing vectors from CSV format files (exporting to CSV format files still gives compiled sequences), and let you change the colors associated with instructions and macros. See "Using the Pattern Generator" (in the online help).

- The Add External Oscilloscope wizard was updated to set up an external oscilloscope module that can import digital channel data from mixed-signal oscilloscopes as well as analog channel data. Also, the update allowed external oscilloscope modules to be correlated with split logic analyzer modules. See " External Oscilloscope Time Correlation and Data Display" (in the online help).

- The external protocol analyzer correlation software supported the N5319A interconnect cable that provides more flexible cross-triggering (via flags). See "External Protocol Analyzer Time Correlation" (in the online help).

- The Status dialog was updated to show more information in the columns of the display and lets you choose which columns are displayed. See Status Dialog (see page 542).

- See Also "Version 03.65 What's New" on page 44

- "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 03.65 What's New

In version 03.65 of the Agilent Logic Analyzer application:

- The new 16951B logic analyzer card was supported in the 16900-series logic analysis system. See 16950/51 Logic Analyzer Notes (see page 656).

- The new "Protocol Development Kit (PDK)" (in the online help) lets you edit and create protocol description files in order to decode, display, and trigger on customized packet data.

- See Also "Version 03.60 What's New" on page 45

- "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

### Version 03.60 What's New

In version 03.60 of the Agilent Logic Analyzer application:

- You could control the new 16901A logic analysis system. See 16900-Series Logic Analysis System Product (see page 617).

- The new 16950B logic analyzer card was supported in the 16900-series logic analysis system. See 16950/51 Logic Analyzer Notes (see page 656).

- The "FPGA Dynamic Probe for Altera FPGAs" (in the online help) add-in software was introduced; it lets you probe signals internal to FPGAs.

- You could set up an external protocol analyzer and a logic analyzer to cross-trigger and make time-correlated measurements (using markers). See "External Protocol Analyzer Time Correlation" (in the online help).

- You could open ALA format configuration files "read-only" in any *Agilent Logic Analyzer* application instance (without licenses for tools, windows, etc. that may be in the configuration). See ALA vs. XML, When to Use Each Format (see page 445).

#### See Also • "Version 03.55 What's New" on page 46

- "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 03.55 What's New

In version 03.55 of the Agilent Logic Analyzer application:

- The E9524A MicroBlaze trace toolset updated the "inverse assembler" (in the online help) to support MicroBlaze version 5.

- See Also "Version 03.50 What's New" on page 47

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 03.50 What's New

In version 03.50 of the Agilent Logic Analyzer application:

- You could control the new 16800-series logic analyzers (see page 614).

- You could view decoded packet data in the new Packet Viewer window. See Analyzing Packet Data (see page 316).

- The "Xilinx FPGA Dynamic Probe" (in the online help) added support for MicroBlaze trace cores (MTC) and there was a new E9524A MicroBlaze trace toolset that provides "inverse assembly" (in the online help).

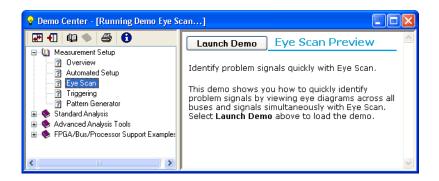

- You could use the new Demo Center (see page 78) application to view logic analysis system feature demonstrations.

- You could use the new "Signal Extractor" (in the online help) tool to extract data from one input bus/signal and place it on multiple output buses/signals. This is useful for extracting I and Q data from simple serial protocols or remultiplexing high-speed digital data that has been demultiplexed onto additional logic analyzer channels.

- You could connect to another logic analysis system without having to go *offline* first. See Connecting to a Logic Analysis System (see page 85).

- There were improvements for multiframe logic analysis systems (see page 446), especially for *performance multiframe configurations*.

- You could rename the bits of a bus and view them when the bus is expanded in the Waveform display window. See To rename the bits of a bus (see page 108).

- You could add separator rows to the Waveform display window. See To insert separator rows (see page 248).

- A graphical trigger was added when viewing module details in the Status dialog (see page 542).

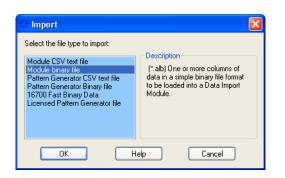

- You could import external data into the logic analysis system from module binary (ALB) format files as well as module CSV format text files. See Using Data Import Modules (see page 227).

- There was a "Force Prestore" option to ensure that the specified percentage of pre-trigger memory is is filled before the logic analyzer begins looking for a trigger. Timing mode used to behave this way while state mode did not. With the "Force Prestore" option, you can choose the desired behavior for both sampling modes. See To specify the trigger position (see page 134).

- You could use the logic analysis system's 10 MHz CLOCK IN input to keep a logic analyzer and an external oscilloscope in sync over long acquisitions. See " Correlation Drift Over Long Acquisitions" (in the online help).

#### 1 What's New

• You could export Listing display window data to 16700 ASCII format files. See To export data to 16700 ASCII format files (see page 215).

See Also

- "Version 03.30 What's New" on page 49

- "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 03.30 What's New

In version 03.30 of the Agilent Logic Analyzer application:

- You could add an external oscilloscope without the time correlation fixture. Default (typical) deskew values for your logic analyzer and oscilloscope models were used. You could still use the time correlation fixture to get the most accurate deskew values for the actual instruments being used. See " External Oscilloscope Time Correlation and Data Display" (in the online help).

- You could import external oscilloscope data and view it faster with import and waveform drawing performance improvements.

- You could activate software licenses, access floating license servers, and borrow floating licenses much easier using the new license manager interface. See Managing Software Licenses (see page 359).

- You could import external data into the logic analysis system and analyze it just like data acquired by logic analyzer modules. See Using Data Import Modules (see page 227).

- You could use these new VBA (Microsoft Visual Basic for Applications) macros and VbaView windows:

- SendToExcel VBA macro that sends captured data to Microsoft Excel.

- *SendToPatternGeneratorModule* VBA macro that sends captured data to a pattern generator module.

- *Timing Compare* VbaView window that compares timing analyzer data with a specified tolerance (plus or minus a number of samples).

See Tools Menu (see page 458), Windows Menu (see page 466), and the online help included with the macro or VbaView window.

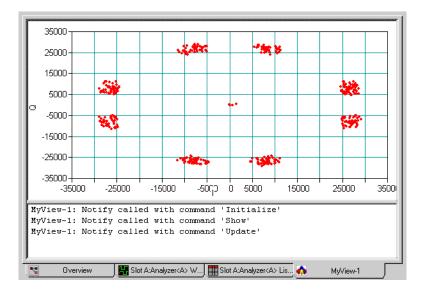

- You could use MatLab in conjunction with the logic analysis system more easily with the new MatLab Connectivity and Analysis package. This licensed package contains these VBA macros and VbaView windows:

- SendToMatLab VBA macro that sends logic analyzer data to MatLab.

- *MatLab Analysis* VbaView window that sends logic analyzer data to MatLab for processing and displays the results in an XY scattergram chart.

- *FFT* VbaView window that performs a Fast Fourier Transform on logic analyzer data and displays the results in a line chart.

See the online help included with the VBA macro and VbaView windows.

• You could use additional remote programming commands with the updated Remote Programming Interface (RPI) compatibility package. See "Using the Remote Programming Interface (RPI)" (in the online help).

- See Also "Version 03.20 What's New" on page 51

- "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 03.20 What's New

In version 03.20 of the Agilent Logic Analyzer application:

- The 16760A logic analyzer card was supported in the 16900-series logic analysis system. See 16760 Logic Analyzer Notes (see page 645).

- You could import data from external oscilloscopes. The Agilent 6000-series oscilloscopes were added to the list of supported oscilloscopes. Also, a new VbaView window let you use the oscilloscope's web interface from within the *Agilent Logic Analyzer* application. See " External Oscilloscope Time Correlation and Data Display" (in the online help).

- The "Serial To Parallel" (in the online help) tool for converting serial data streams into parallel bus data was introduced.

- The "Xilinx FPGA Dynamic Probe" (in the online help) add-in software was updated to support automatic set up features.

- Pattern generator compiled vectors were saved in XML format configuration files as well as ALA format configuration files. See "Using the Pattern Generator" (in the online help).

- Microsoft Visual Basic for Applications (VBA) macros and VbaView windows were saved in XML format configuration files as well as ALA format files. See "Distributing VBA Code" (in the online help).

- You could disable multiple modules at the same time and choose whether or not to remove their connections to tools and display windows. When you leave connections, buses/signals associated with disabled modules remain in display windows, but they have no data. See To disable and enable modules (see page 98).

#### See Also • "Version 03.00 What's New" on page 52

- "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 03.00 What's New

In version 03.00 of the Agilent Logic Analyzer application:

- The 16720A pattern generator card was supported in the 16900-series logic analysis system. See "Using the Pattern Generator" (in the online help).

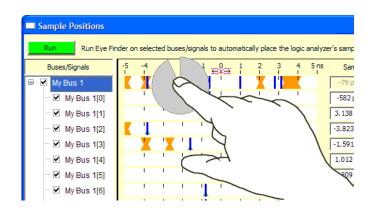

- The *eye finder* feature for automatically adjusting state mode sampling positions was enhanced to automatically determine optimal threshold voltage settings as well. See Understanding State Mode Sampling Positions (see page 424).

- Microsoft Visual Basic for Applications (VBA) was been integrated into the *Agilent Logic Analyzer* application to let you easily automate measurements and add custom control and data visualization tools. See Extending Capture Capability with VBA (see page 217) and Extending Data Visualization/Analysis with VBA (see page 357).

#### See Also • "Version 02.50 What's New" on page 53

- "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 02.50 What's New

In version 02.50 of the Agilent Logic Analyzer application:

- The *eye finder* feature for automatically adjusting sampling positions in state mode was made available for 1680- and 1690-series logic analyzers (this feature was previously only available for logic analyzers in the 16900-series logic analysis system).

- The "Xilinx FPGA Dynamic Probe" (in the online help) add-in software was introduced; it lets you probe signals internal to FPGAs.

- The "General Purpose Probe" (in the online help) add-in software was added; it lets you set up probe definitions in order to:

- Cause device under test pin/pad numbers to appear in the Buses/Signals setup tab.

- Document logic analyzer pod connections.

- Prepare for importing netlist files to automatically define buses/signals.

- The "PCI Express Analysis Probe" (in the online help) add-in software (for the N4220A/B PCI Express analysis probe) was introduced, and the new Packet Decoder tool was used to decode PCI Express bus data.

- In the window, a separate column for probes (general purpose, FPGA dynamic, PCI Express, etc.) was added, and you were able to access probe properties from there.

- See Also "Version 02.00 What's New" on page 54

- "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 02.00 What's New

In version 02.00 of the Agilent Logic Analyzer application:

- You could control the new 16900-series logic analysis system (see page 617) and access the new features associated with it. The same *Agilent Logic Analyzer* application controls the 1680- and 1690-series logic analyzers and can be used by itself on Windows XP/2000 computers for *remote access* (see page 85) or *offline analysis* (see page 233).

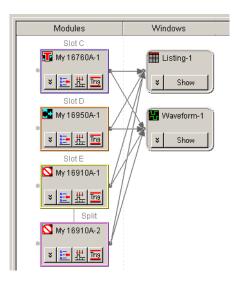

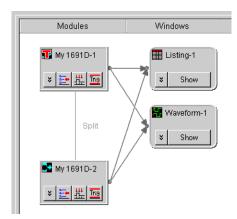

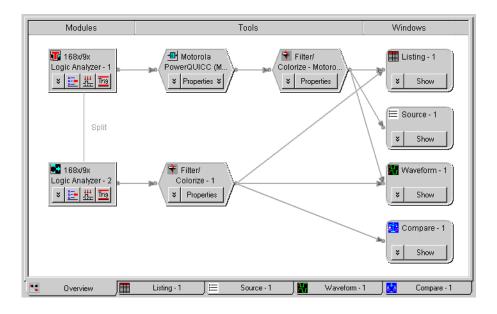

- The ability to split logic analyzer modules was added. This is useful for analyzing buses with different clocks.

With multiple logic analyzer modules, the ability to identify which is the system trigger and specify the skew between the modules was added.

- The *eye finder* feature for automatically adjusting sampling positions in state mode was added for logic analyzers in the 16900-series logic analysis system.

- The ability to load program symbols from compiler-generated output files was added.

- The ability to display the high-level language source code associated with captured data and set up triggers based on source code locations was added in the new Source display window.

- A new dual-sample state sampling clock mode, often used to capture DDR memory bus activity, was added.

- The Netlist Import dialog was reorganized and a separate dialog for defining probes was added.

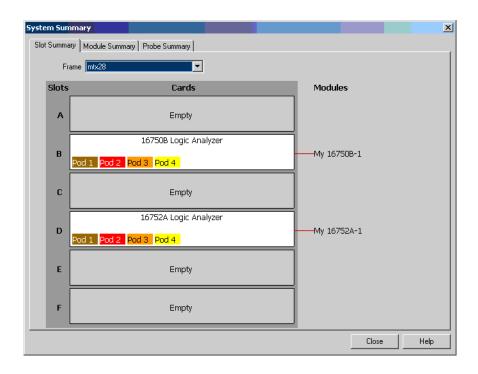

- New System Summary and Status dialogs for displaying information about the logic analysis system were added.

- Performance improvements were made: waveform drawing became much faster, and the *Agilent Logic Analyzer* application was made into a multi-threaded application.

- See Also "Version 01.40 What's New" on page 55

- "Version 01.20 What's New" on page 57

- "Version 01.10 What's New" on page 58

# Version 01.40 What's New

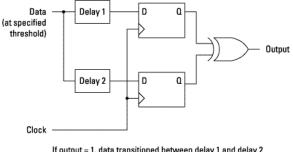

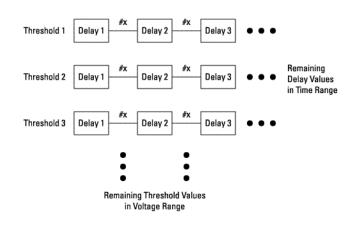

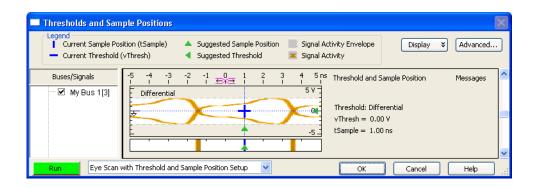

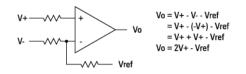

Version 01.40 of the Agilent Logic Analyzer application: