# **DDR Setup Assistant**

**Online Help**

#### **Notices**

© Agilent Technologies, Inc. 2014

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

#### **Sales and Technical Support**

To contact Agilent for sales and technical support, refer to the "support" links on the following Agilent web resources:

www.agilent.com/find/(product-specific information and support, software and documentation updates)

www.agilent.com/find/assist (worldwide contact information for repair and service)

Information on preventing damage to your Agilent equipment can be found at www.agilent.com/find/tips.

#### **Software Release**

Version 05.80.0000

#### **Edition**

January 2014

Available in electronic format only

Agilent Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

#### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

#### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

#### **Safety Notices**

#### **CAUTION**

A **CAUTION** notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a **CAUTION** notice until the indicated conditions are fully understood and met.

#### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

## DDR Setup Assistant—At a Glance

The DDR Setup Assistant is a wizard-like application that helps you set up your logic analyzer properly for DDR/LPDDR data capture and analysis.

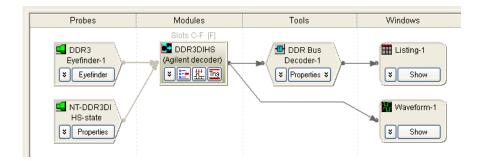

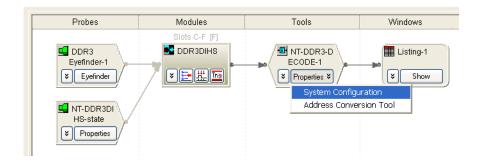

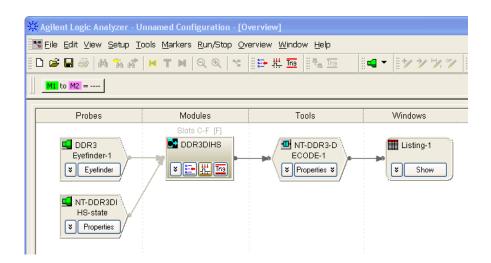

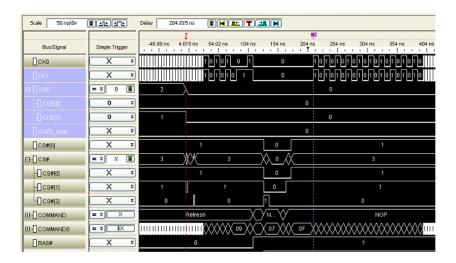

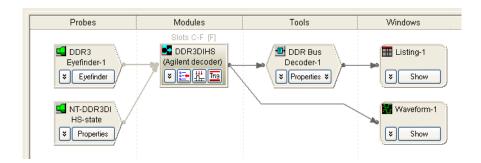

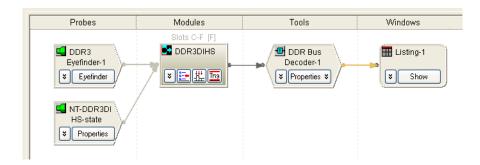

Once you have completed the set up steps using the DDR Setup Assistant, the *Agilent Logic and Protocol Analyzer* application will have the appropriate Probes, Modules, Tools, and Windows set up, similar to those shown in the example Overview tab below.

Typically, the resulting Overview tab will contain:

- DDR3 Eyefinder used to set up the appropriate sample positions for capturing DDR data.

- General purpose probe tool shows how to connect the probe to logic analyzer pods.

- Four-card logic analyzer module (16962A or 16960A) or U4154A Logic Analyzer module.

- DDR Bus Decoder decodes the captured data.

- Listing window to display decoded data.

- Optional Waveform window to display state or timing waveforms.

It is best to add Waveform windows immediately after the logic analyzer module because, when displaying large amounts of waveform data, decoding can slow down the waveform display.

See • "In This Guide" on page 5

#### In This Guide

For an overview and list of features, see: "DDR Setup Assistant—At a Glance" on page 3

First, this guide describes the options for probing DDR devices and the logic analysis system hardware and software required before you can use the DDR Setup Assistant.

- Chapter 1, "Options for Probing DDR Devices," starting on page 11

- Chapter 2, "Before Using the DDR Setup Assistant," starting on page 27

Next, this guide provides more in-depth information about the steps taken when using the DDR Setup Assistant:

- "Step Specify Input Parameters" on page 35

- "Step Verify Software Installation" on page 36

- "Step Load Configuration File" on page 37

- "Step Do Hardware Setup" on page 40

- "Step Set Initial Thresholds" on page 42

- "Step Set Sample Positions of Clk/CS Signals (only applicable to U4154A Logic Analyzer)" on page 43

- "Step Set Sample Positions of Command/Addr Signals (only applicable to U4154A Logic Analyzer)" on page 45

- "Step Set Sample Positions of Ctrl/Addr Signals (not applicable to U4154A Logic Analyzer)" on page 47

- "Step Find Latency Values" on page 49

- "Step Set Sample Positions of Data-related Signals (not applicable to U4154A logic analyzer)" on page 60

- "Step Set Sample Positions of Data Read/Write (only applicable to U4154A Logic Analyzer)" on page 61

- "Step Save Setup" on page 65

- "Setup Complete" on page 66

Then, there is more in-depth information on using the logic analyzer's automated Thresholds and Sample Positions set up (also known as normal logic analyzer *eye finder*), using DDR3 Eyefinder, and validating DDR setups once you have completed the sampling position set up.

- Chapter 4, "Setting Up Thresholds and Sample Positions on DDR Address/Control Signals," starting on page 67

- Chapter 5, "Using DDR3 Eyefinder," starting on page 75

- Chapter 6, "Using Eyescan (for U4154A Logic Analyzer Module)," starting on page 105

- Chapter 7, "Validating the DDR Setup," starting on page 107

Finally, this guide introduces you to the other tools used for capturing and analyzing data from DDR systems and provides pointers to additional documentation.

- Chapter 8, "Capturing Data (Triggering)," starting on page 109

- Chapter 9, "Decoding Captured Data," starting on page 113

For a printable version of this online help, see:  $\begin{cases} \begin{cases} \begin$

#### See Also

- DDR probe manuals.

- DDR Bus Decoder Online Help

- DDR Compliance Tool online help.

## **Contents**

|   | DDR Setup Assistant—At a Glance 3                                                                                                                                                                                   |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | In This Guide 5                                                                                                                                                                                                     |

| 1 | Options for Probing DDR Devices                                                                                                                                                                                     |

|   | DDR3 DIMM Interposers 12 FS2352 1867 DDR3 DIMM Probe from FuturePlus 13 Nexus DDR3 DIMM Interposer 13 N4835A (FS2351) DDR3 DIMM Interposer (Discontinued) 14 N4821B (FS2350) DDR3 DIMM Interposer (Discontinued) 15 |

|   | DDR3 SODIMM Interposers 16 FS2354 DDR3 SODIMM Interposer 16 Nexus DDR3 SODIMM Interposer 17                                                                                                                         |

|   | DDR3 BGA Probes 18 W3633A DDR3 BGA x8 Probe 18 W3631A DDR3 BGA x16 Probe 19                                                                                                                                         |

|   | DDR3 Midbus Probes 20 N4834A DDR3 Midbus Probe (Discontinued) 20                                                                                                                                                    |

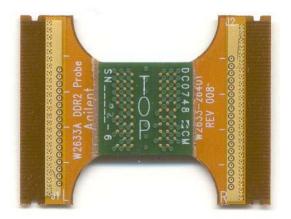

|   | DDR2 BGA Probes 21<br>W2633A/B, W2634A DDR2 BGA x8 Probe 21<br>W2631A/B, W2632A DDR2 BGA x16 Probe 22                                                                                                               |

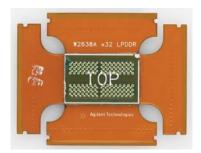

|   | LPDDR BGA Probes 23 W2638A LPDDR BGA x32 Probe 23 W2637A LPDDR BGA x16 Probe 23                                                                                                                                     |

|   | Custom Midbus Probing 24  Soft Touch / Soft Touch Pro Embedded Custom Midbus Probing 24                                                                                                                             |

| 2 | Before Using the DDR Setup Assistant                                                                                                                                                                                |

|   | Logic Analysis System Hardware Requirements 28                                                                                                                                                                      |

|   | Installing Required and Optional Software 29                                                                                                                                                                        |

|   | Tuning Your DDR DUT to Make the Best Measurements 30                                                                                                                                                                |

|   | Setting Up Read and Write Traffic in the DUT 31                                                                                                                                                                     |

#### 3 Using the DDR Setup Assistant

```

Starting the DDR Setup Assistant

34

Step - Specify Input Parameters

35

Step - Verify Software Installation

36

Step - Load Configuration File

Step - Do Hardware Setup

40

Step - Set Initial Thresholds

42

Step - Set Sample Positions of Clk/CS Signals (only applicable to U4154A Logic

Analyzer)

Step - Set Sample Positions of Command/Addr Signals (only applicable to U4154A Logic

Analyzer)

Step - Set Sample Positions of Ctrl/Addr Signals (not applicable to U4154A Logic

Analyzer)

If there are problems with finding Ctrl/Addr sample positions

48

Step - Find Latency Values

49

Taking a Mode Register Settings (MRS) Trace

50

53

Setting Latency Values in DDR Bus Decoder

Setting Latency Values in DDR3 Eyefinder

Setting Latency Values in Eyescan

Step - Set Sample Positions of Data-related Signals (not applicable to U4154A logic

analyzer)

Step - Set Sample Positions of Data Read/Write (only applicable to U4154A Logic

Analyzer)

To find and set sample positions for DDR4 Data related signals

62

Step - Save Setup

65

Setup Complete

66

```

#### 4 Setting Up Thresholds and Sample Positions on DDR Address/Control Signals

```

Setting Up Thresholds and Sample Positions 68

Solving Problems with Thresholds and Sample Positions Set Up 72

No eye finder or eye scan eyes for Address and Command 72

Clock edges "too close together" error message on Run 72

```

#### 5 Using DDR3 Eyefinder

```

Getting Started with DDR3 Eyefinder (for 16962A/16960A)

76

Before Running DDR3 Eyefinder

76

Your First DDR3 Eyefinder Scan (16962A logic analyzers only)

76

Setting Scan Options

87

Setting DDR Bus Specifications

87

Setting Scan Mode

Setting Scan Options

89

Performing Scans

Setting Sample Positions

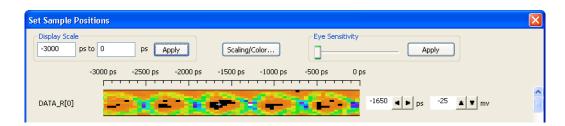

Adjusting the Display Scale

95

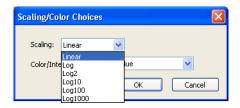

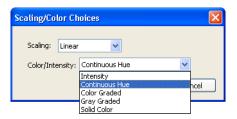

Changing the Time Bucket Scaling and Colors

95

Adjusting the Eye Sensitivity

97

Adjusting Sample Positions

98

Viewing Signal Swing vs. Time

99

Solving DDR3 Eyefinder Problems

100

If scans stick on Runs in DDR3 Eyefinder

If there are no transitions in DDR3 Eyefinder

100

If eyes show tri-stating

If eyes are closed

If there are multiple eyes

102

If eye scan results are noisy

103

```

#### 6 Using Eyescan (for U4154A Logic Analyzer Module)

#### 7 Validating the DDR Setup

Validating Data in the Trace 108

#### 8 Capturing Data (Triggering)

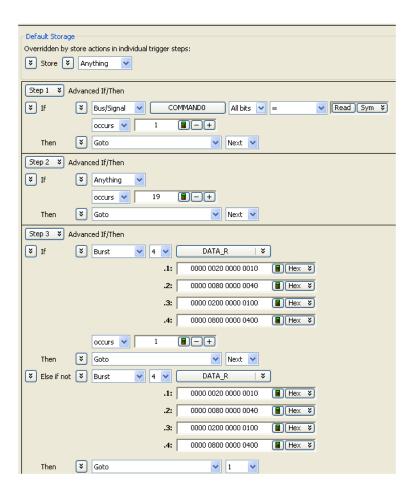

Recalling DDR Favorite Triggers 110

Triggering on Valid Commands 111

Burst Triggering 112

#### 9 Decoding Captured Data

DDR Bus Decoder 114

- A Setting Data Sample Positions with the 1695x Logic Analyzers

- **B DDR Glossary**

Index

## **Options for Probing DDR Devices**

There are several different Agilent and third-party options for probing a DDR device under test (DUT).

#### DDR3

- "DDR3 DIMM Interposers" on page 12:

- "FS2352 1867 DDR3 DIMM Probe from FuturePlus" on page 13

- "Nexus DDR3 DIMM Interposer" on page 13

- "N4835A (FS2351) DDR3 DIMM Interposer (Discontinued)" on page 14

- "N4821B (FS2350) DDR3 DIMM Interposer (Discontinued)" on page 15

- "DDR3 SODIMM Interposers" on page 16:

- "FS2354 DDR3 SODIMM Interposer" on page 16

- "Nexus DDR3 SODIMM Interposer" on page 17

- "DDR3 BGA Probes" on page 18:

- "W3633A DDR3 BGA x8 Probe" on page 18

- "W3631A DDR3 BGA x16 Probe" on page 19

- "DDR3 Midbus Probes" on page 20:

- "N4834A DDR3 Midbus Probe (Discontinued)" on page 20

#### DDR2

- "DDR2 BGA Probes" on page 21:

- "W2633A/B, W2634A DDR2 BGA x8 Probe" on page 21

- "W2631A/B, W2632A DDR2 BGA x16 Probe" on page 22

#### **LPDDR**

- "LPDDR BGA Probes" on page 23:

- "W2638A LPDDR BGA x32 Probe" on page 23

- "W2637A LPDDR BGA x16 Probe" on page 23

#### **Custom**

- "Custom Midbus Probing" on page 24:

- "Soft Touch / Soft Touch Pro Embedded Custom Midbus Probing" on page 24

## **DDR3 DIMM Interposers**

- "FS2352 1867 DDR3 DIMM Probe from FuturePlus" on page 13

- "Nexus DDR3 DIMM Interposer" on page 13

- "N4835A (FS2351) DDR3 DIMM Interposer (Discontinued)" on page 14

- "N4821B (FS2350) DDR3 DIMM Interposer (Discontinued)" on page 15

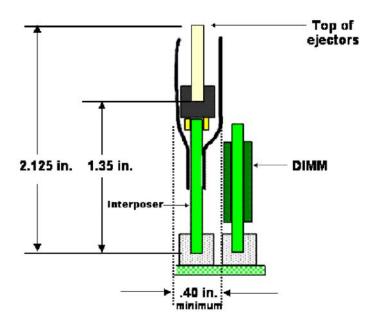

#### Handling DIMM Interposers

Handle interposers carefully.

- Provide strain relief for cables.

- Store and ship flat.

#### Using DIMM Interposers

- 1 First, make sure that the device under test boots without the interposer.

- 2 Power down the device under test.

- **3** Insert interposer into the DIMM socket.

- 4 Fan headers out on either side of interposer.

- **5** Insert the DIMM into the interposer.

- 6 Make connections to the logic analyzer pod cables as shown in the configuration file's general-purpose probe tool.

#### FS2352 1867 DDR3 DIMM Probe from FuturePlus

FS2352 1867 DIMM probe from FuturePlus works with 16962A logic analyzer modules only.

## Configuration Files for FS2352

The default location for FuturePlus configuration files is: C:\Documents and Settings\All Users\Shared Documents\Agilent Technologies\Logic Analyzer\Default Configs\FuturePlus

For More Information

• Search for "FS2352" on the "FuturePlus web site".

### **Nexus DDR3 DIMM Interposer**

#### 1 Options for Probing DDR Devices

The Nexus DDR3 DIMM interposer works with 16962A logic analyzer modules only.

Configuration Files for Nexus DDR3 DIMM Interposer The default location for Nexux configuration files is: C:\Documents and Settings\All Users\Shared Documents\Agilent Technologies\Logic Analyzer\ Default Configs\Nexus

For More Information

• See "NT-DDR3DIHS information on the Nexus Technology web site".

### N4835A (FS2351) DDR3 DIMM Interposer (Discontinued)

N4835A (FS2351) works with 16960A or 16962A logic analyzer modules.

## Configuration File for N4835A

There is one configuration file for the N4835A DDR3 DIMM interposer at all data rates.

\* CK0 is double probed on N4835A. You can run eye finder and eye scan (that is, logic analyzer Thresholds and Sample Positions set up) on the sample of CK0 that is not used as the actual clock.

#### **CAUTION**

Make sure you have the proper N4835A configuration file for the N4835A (FS2351) interposer. While the pod connections are the same as with the N4821B (FS2350) interposer's 1066/1333 configuration, the signal mapping is not the same!

See "To load a configuration file" (in the online help).

## For More Information

• See *Agilent N4835A DDR3 DIMM Interposer Installation Guide* which can be found on the "Agilent web site".

### N4821B (FS2350) DDR3 DIMM Interposer (Discontinued)

N4821B (FS2350) works with 16960A or 16962A logic analyzer modules.

## Configuration Files for N4821B

There is one configuration file for the 16962A logic analyzer at all data rates. There are two configuration files for the 16960A logic analyzer module: one for 800/1600 data rates, and one for 1066/1333 data rates.

See "To load a configuration file" (in the online help).

#### For More Information

• Search for "FS2350" on the "FuturePlus web site".

## **DDR3 SODIMM Interposers**

- "FS2354 DDR3 SODIMM Interposer" on page 16

- "Nexus DDR3 SODIMM Interposer" on page 17

### FS2354 DDR3 SODIMM Interposer

FS2354 SODIMM works with 16962A logic analyzer modules only.

## Configuration Files for FS2354

The default location for FuturePlus configuration files is: C:\Documents and Settings\All Users\Shared Documents\Agilent Technologies\Logic Analyzer\Default Configs\FuturePlus

## For More Information

• Search for "FS2354" on the "FuturePlus web site".

#### **Nexus DDR3 SODIMM Interposer**

Nexus DDR3 SODIMM interposer works with 16962A logic analyzer modules only.

Configuration Files for Nexus DDR3 SODIMM Interposer The default location for Nexux configuration files is: C:\Documents and Settings\All Users\Shared Documents\Agilent Technologies\Logic Analyzer\ Default Configs\Nexus

For More Information

• See "NT-DDR3SOIHS information on the Nexus Technology web site".

#### **DDR3 BGA Probes**

- "W3633A DDR3 BGA x8 Probe" on page 18

- "W3631A DDR3 BGA x16 Probe" on page 19

The DDR3 BGA probes work with 16950A/B or 16962A logic analyzer modules, and there separate configuration files for each. There are also separate configuration files for the x8 and x16 probes.

#### W3633A DDR3 BGA x8 Probe

Configuration Files for W3633A Probe

See "To load a configuration file" (in the online help).

For More Information, See

• Agilent W3630 Series DDR3 DRAM BGA Probes Installation Guide which can be found on the "Agilent web site".

#### W3631A DDR3 BGA x16 Probe

Configuration Files for W3631A Probe

See "To load a configuration file" (in the online help).

For More Information, See

• Agilent W3630 Series DDR3 DRAM BGA Probes Installation Guide which can be found on the "Agilent web site".

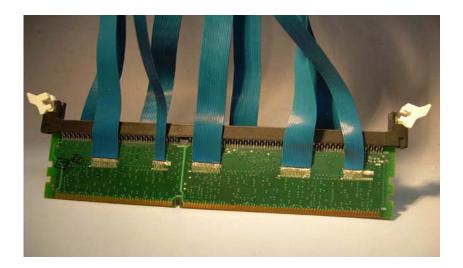

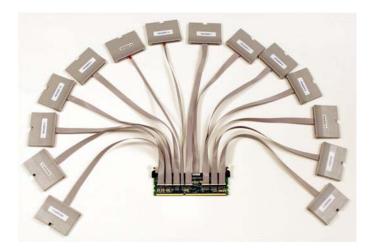

#### **DDR3 Midbus Probes**

DDR3 midbus probes require special footprints to be designed into the device under test, and they require double probing. Limited quantities of these probes were available.

• "N4834A DDR3 Midbus Probe (Discontinued)" on page 20

#### N4834A DDR3 Midbus Probe (Discontinued)

For embedded DDR3 design or validation board design with no constraints on board spaces, the N4834A double probed soft touch probe can be used for midbus probing. The N4834A comes in sets of 4 double probed soft touch probes for connection to four footprints on the board.

The N4834A DDR3 midbus probe works with 16960A or 16962A logic analyzer modules.

Configuration Files for N4834A Probe

See "To load a configuration file" (in the online help).

For More Information

• Search for "N4834A" on the "Agilent web site".

#### **DDR2 BGA Probes**

- "W2633A/B, W2634A DDR2 BGA x8 Probe" on page 21

- "W2631A/B, W2632A DDR2 BGA x16 Probe" on page 22

The DDR2 BGA probes work with 16950A/B or 16962A logic analyzer modules, and there separate configuration files for each. There are also separate configuration files for the x8 and x16 probes.

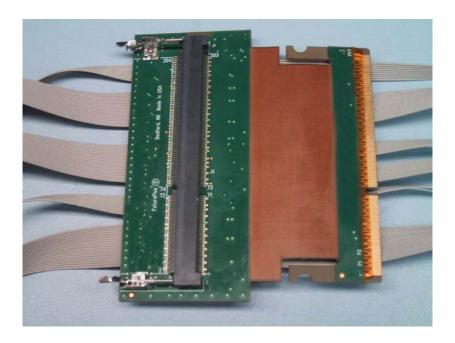

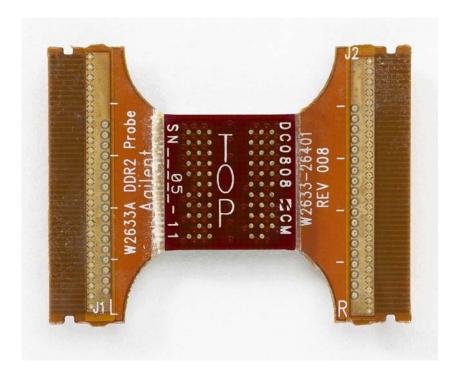

#### W2633A/B, W2634A DDR2 BGA x8 Probe

Configuration Files for W2633A/B, W2634A Probes See "To load a configuration file" (in the online help).

For More Information, See

• Agilent W2630 Series DDR2 DRAM BGA Probes Installation Guide which can be found on the "Agilent web site".

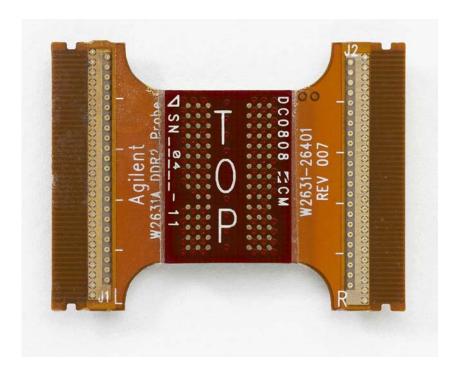

## W2631A/B, W2632A DDR2 BGA x16 Probe

Configuration Files for W2631A/B, W2632A Probes See "To load a configuration file" (in the online help).

For More Information, See

• Agilent W2630 Series DDR2 DRAM BGA Probes Installation Guide which can be found on the "Agilent web site".

#### **LPDDR BGA Probes**

- "W2638A LPDDR BGA x32 Probe" on page 23

- "W2637A LPDDR BGA x16 Probe" on page 23

The LPDDR BGA probes work with 16950A/B or 16962A logic analyzer modules, and there separate configuration files for each.

#### W2638A LPDDR BGA x32 Probe

Configuration Files for W2638A Probe

See "To load a configuration file" (in the online help).

For More Information, See

• W2637A and W2638A LPDDR BGA Probes / W2639A Oscilloscope Adapter Board User's Guide which can be found on the "Agilent web site".

#### W2637A LPDDR BGA x16 Probe

Configuration Files for W2637A Probe

See "To load a configuration file" (in the online help).

For More Information, See

• W2637A and W2638A LPDDR BGA Probes / W2639A Oscilloscope Adapter Board User's Guide which can be found on the "Agilent web site".

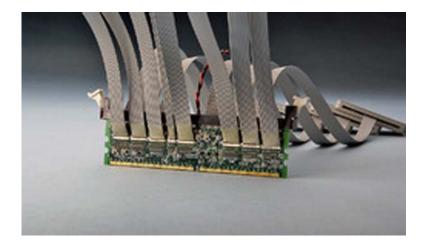

### **Custom Midbus Probing**

For custom midbus probing, you can design Soft Touch or Soft Touch Pro footprints into your device under test and route signals to the footprint pads.

• "Soft Touch / Soft Touch Pro Embedded Custom Midbus Probing" on page 24

#### Soft Touch / Soft Touch Pro Embedded Custom Midbus Probing

You can design Soft Touch or Soft Touch Pro footprints into your device under test (DUT) and route signals to the footprint pads. Because this type of probing is *custom*, DUT designs are unique. However, there are some common things to consider.

Because DDR data reads and writes occur at different times relative to the bus (and sampling) clock, you must use the logic analyzer's dual sample sampling clock mode (see "Dual Sample Sampling Clock Mode" (in the online help)). This affects how signals are probed and mapped to logic analyzer pods.

Other considerations for embedded Soft Touch footprints for 16962A or 16960A logic analyzers:

- The CKO, Address, and Control bits should be placed on one Soft Touch footprint. This is a requirement for DDR3 Eyefinder. Also, you must connect the address and control signals to a different logic analyzer module than the data /strobe signals. Solutions for DDR logic analysis require a module minimum of two logic analyzer modules.

- The CKO signal must be probed differentially and must be connected to the pod 1 clock of the clocking module (this is the second card up from the bottom of the mainframe).

- The CKE0 signal should be connected to the clock input on pod 2 of the master module. When setting up the state sampling clock options in the logic analyzer, select:

- CKE0 latched high for capture out of reset.

- CKE0 enabled high as clock qualifier.

- Make sure there are no signal stubs!

- Optional: consider routing a copy of the CS#0 signal to the Pod 4 clock input on the master module.

- The minimum signals required for DDR logic analysis tools are:

- CKO, COMMAND, CS#, Data\_W, Data\_R, CKE\*, BA, ADDR, RowADDR, and ColADDR.

- Custom triggers may require additional signals.

#### Configuration Files for Soft Touch Probes

With custom probing, you will likely have custom configuration files. Be sure to include a general-purpose probe tool in your Overview configuration to describe how logic analyzer pod connectors should be connected to the probes.

To simplify the procedure of custom configuration file creation, Agilent provides the DDR/LPDDR Custom Configuration Creator tool. The tool ensures that all the layout information needed by DDR/LPDDR Decoder is included in the created configuration file. This tool is a part of the Agilent DDR Setup Assistant and Eyefinder software package. Therefore, the tool is available only after you install this package. To know more about this tool, refer to its online help that gets installed with this tool's software.

## For More Information, See

- Agilent Technologies E5400-Pro Series Soft Touch Connectorless Probes User's Guide which can be found on the "Agilent web site".

- Agilent Technologies Soft Touch Connectorless Probes User's Guide which can be found on the "Agilent web site".

1 Options for Probing DDR Devices

DDR Setup Assistant Online Help

## **Before Using the DDR Setup Assistant**

Logic Analysis System Hardware Requirements 28

Installing Required and Optional Software 29

Tuning Your DDR DUT to Make the Best Measurements 30

Setting Up Read and Write Traffic in the DUT 31

Once you have chosen a solution for probing your DDR device, you must make sure you have the required logic analysis system hardware and software. This includes any necessary probe to logic analyzer cable adapters.

There are also some things you can do to prepare your DDR device under test in order to make the best measurements.

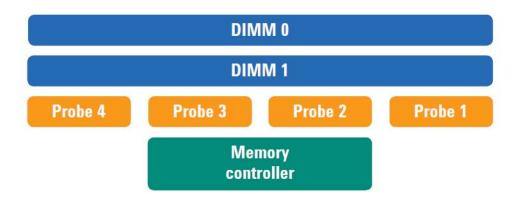

## **Logic Analysis System Hardware Requirements**

To capture DDR Command, Address, Control, and Data signals, a four-card, 68-channel per card, logic analyzer card set with sufficient state analysis speed is required. The 16962A and 16960A logic analyzer cards meet these requirements.

A six-slot logic analysis system frame is required for the four-card logic analyzer. The 16902B logic analysis system frame meets the requirement.

Besides these, you can also use the 136 channel U4154A Logic Analyzer module installed in the Agilent AXIe chassis to capture DDR signals.

### **Installing Required and Optional Software**

#### NOTE

While the DDR Setup Assistant works with the *Agilent Logic Analyzer* application on a computer remotely connected to logic analyzer hardware, we recommend you run the DDR Setup Assistant on the logic analysis system that contains the logic analyzer hardware. This is because the logic analyzer's automated Thresholds and Sample Positions set up (also known as logic analyzer *eye finder*) and DDR3 Eyefinder run faster in this configuration.

You can use the Windows operating system's Remote Desktop Connection feature to log into the logic analysis system that has the logic analyzer hardware. The Remote Desktop Connection provides good performance.

Before you begin using the DDR Setup Assistant, make sure the required software (and any desired optional software) is installed.

This software can be downloaded from the Agilent web site at: "www.agilent.com/find/la-sw-download"

## Required Software

The following software is required in order to use the DDR Setup Assistant:

- Agilent Logic Analyzer Application Software, version 04.00 or higher.

- DDR2 and DDR3 Bus Decoder (B4621B, requires a license), version 04.00 or higher. This software decodes the captured signals, showing commands, cycle types, etc. DDR configuration files are included with the bus decoder and many of them assume the bus decoder is present.

- DDR3 Eyefinder, version 04.00 or higher. This software is necessary to set sample positions for Data signals.

- If you have a third-party (non-Agilent) probe, there may be third-party software that is also required.

#### Optional DDR Tools

The following software is optional but is useful for DDR analysis:

• DDR2/3 Protocol Compliance and Analysis Tool (B4622B, requires a license), version 04.00 or higher. This is an automated test application that evaluates captured LPDDR/LPDDR2 and DDR/DDR2/DDR3 data against a set of user-defined limits to help you validate that a memory system is operating properly. When used with the U4154A module, it can evaluate LPDR3 and DDR4 data as well.

## **Tuning Your DDR DUT to Make the Best Measurements**

There are a couple things you can do to prepare your DDR device under test for making measurements:

- Turn off data scrambling.

- Turn off power management (for initial measurements).

## **Setting Up Read and Write Traffic in the DUT**

READ and WRITE traffic in the DDR device under test (DUT) is required for both Read and Write signal sampling set up. For example:

- Random pattern data tests:

- Memtest 86 test #7.

- Memory test with alternating patterns:

- Memtest 86 test #5.

- · Video clips.

2 Before Using the DDR Setup Assistant

# Using the DDR Setup Assistant

Starting the DDR Setup Assistant 34 Step - Specify Input Parameters 35 Step - Verify Software Installation 36 Step - Load Configuration File 37 Step - Do Hardware Setup 40 Step - Set Initial Thresholds 42 Step - Set Sample Positions of Clk/CS Signals (only applicable to U4154A Logic Analyzer) 43 Step - Set Sample Positions of Command/Addr Signals (only applicable to U4154A Logic Analyzer) 45 Step - Set Sample Positions of Ctrl/Addr Signals (not applicable to U4154A Logic Analyzer) 47 Step - Find Latency Values 49 Step - Set Sample Positions of Data-related Signals (not applicable to U4154A logic analyzer) 60 Step - Set Sample Positions of Data Read/Write (only applicable to U4154A Logic Analyzer) 61 Step - Save Setup 65 Setup Complete 66

### **Starting the DDR Setup Assistant**

#### NOTE

While the DDR Setup Assistant works with the *Agilent Logic Analyzer* application on a computer remotely connected to logic analyzer hardware, we recommend you run the DDR Setup Assistant on the logic analysis system that contains the logic analyzer hardware. This is because the logic analyzer's automated Thresholds and Sample Positions set up (also known as logic analyzer *eye finder*) and DDR3 Eyefinder run faster in this configuration.

You can use the Windows operating system's Remote Desktop Connection feature to log into the logic analysis system that has the logic analyzer hardware. The Remote Desktop Connection provides good performance.

1 After installing the DDR Setup Assistant, double-click the **DDR Setup** Assistant icon on your desktop to start the DDR Setup Assistant.

The DDR Setup Assistant automatically starts the *Agilent Logic Analyzer* application if it is not already started.

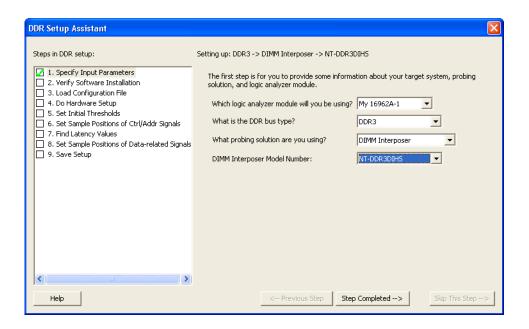

## **Step - Specify Input Parameters**

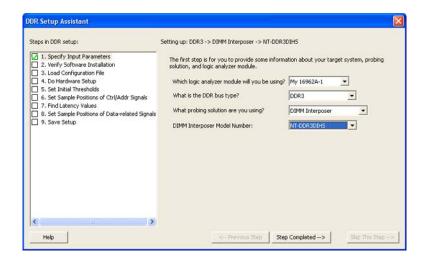

In this step, you give the DDR Setup Assistant relevant information about your DDR test setup.

- 1 Select the name of the logic analyzer module that will be used to capture DDR signals.

- 2 Select the DDR bus type.

- **3** Specify your **probing solution** (see Chapter 1, "Options for Probing DDR Devices," starting on page 11).

Depending on the probing solution you select, you may have additional input parameters to specify. For example:

- When you select the **BGA** probing solution, you have an additional selection for your **DRAM type and data width**.

- When you select the **DIMM Interposer** probing solution, there is an additional selection for the model number.

- When you select the **Softtouch** probing solution, there are no other input parameters to specify.

**4** When you are finished selecting input parameters, click **Step Completed** -->.

The selections you make in this step identify your setup for the automated DDR Setup Assistant actions that follow.

Next • "Step - Verify Software Installation" on page 36

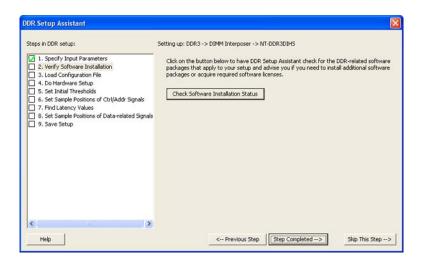

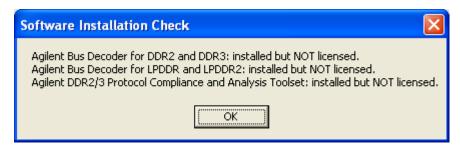

### **Step - Verify Software Installation**

In this step, the DDR Setup Assistant checks to see if the required and optional DDR analysis software has been installed.

1 Click Check Software Installation Status.

When the check is complete, an information with the software installation status appears.

- **2** If you need to install software:

- a Close the DDR Setup Assistant.

- **b** Close the *Agilent Logic Analyzer* application.

- c Install the software (see "Installing Required and Optional Software" on page 29).

- d Restart the Agilent Logic Analyzer application.

- e Restart the DDR Setup Assistant.

- f Continue with the DDR set up steps.

- 3 Click Step Completed -->.

Next • "Step - Load Configuration File" on page 37

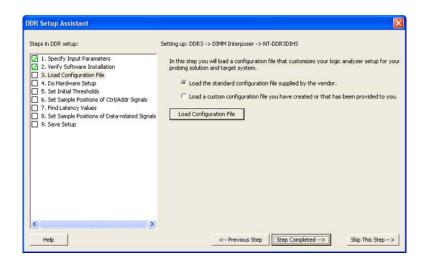

## **Step - Load Configuration File**

In this step, the DDR Setup Assistant loads the selected XML configuration file.

1 Select whether you want to load an Agilent-supplied standard configuration file (if you are using an Agilent probing solution) or a custom configuration file (if you are using a custom probing solution).

If you select to load a standard configuration file, the DDR Setup Assistant automatically tries to locate and load an appropriate configuration file based on the input parameters you selected in the first step. The file is loaded from the set of standard configuration files. The default location for these standard configuration files is:

$C:\Documents\ and\ Settings\All\ Users\Documents\Agilent\ Technologies\ Logic\ Analyzer\Default\ Configs\Agilent\$

If you select to load a custom configuration file, the DDR Setup Assistant allows you to navigate to the custom configuration file location and select it for loading.

NOTE

To simplify the procedure of custom configuration file creation, Agilent provides the DDR/LPDDR Custom Configuration Creator tool. The tool ensures that all the layout information needed by DDR/LPDDR Decoder is included in the created configuration file. This tool is a part of the Agilent DDR Setup Assistant and Eyefinder software package. Therefore, the tool is available only after you install this package.

To know more about this tool, refer to its online help that gets installed with this tool's software.

#### 2 Click Load Configuration File.

- If the DDR Setup Assistant cannot find the configuration file for a probe, an error dialog is displayed, and you are given an opportunity to browse for the file.

- If you are using a Soft Touch probing solution, a file browser appears for you to select the configuration file for your custom probing solution.

- In some cases, you may know of a modified configuration file that should be used for a particular probing setup. In this case, you can manually load the configuration file.

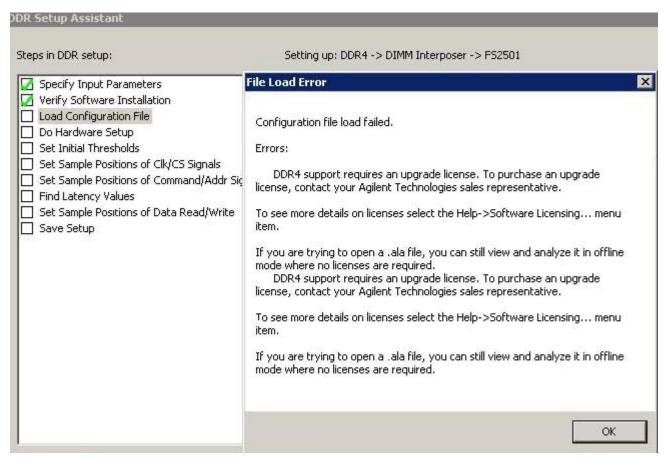

- If you selected DDR4 or LPDDR3 as the DDR Bus Type in Step 1 of the wizard and you do not have the B4621B (for DDR) and B4623B (for LPDDR) software licenses installed, then you will not be able to load a standard or a custom DDR4/LPDDR3 configuration file in this step. In such a situation, the following error message will be displayed. To get DDR4 and LPDDR3 support, you must purchase the B4621B and B4623B license respectively.

3 If necessary, navigate to the configuration file.

The default location for standard configuration files is:

C:\Documents and Settings\All Users\Documents\Agilent Technologies\Logic Analyzer\Default Configs\Agilent\

Then, select the file and click Open.

4 Click Step Completed -->.

Configuration files typically include:

- A general purpose probe tool to define the mapping between device under test signals and logic analyzer pods. If the configuration file doesn't include one, you can add it yourself. See "To define probes" (in the online help).

- A DDR Bus Decoder tool for decoding the captured data. If the configuration file doesn't include one, you can add it yourself. See "To add new tools" (in the online help).

For more information about the configuration files provided for the different DDR probing options, see Chapter 1, "Options for Probing DDR Devices," starting on page 11.

Next • "Step - Do Hardware Setup" on page 40

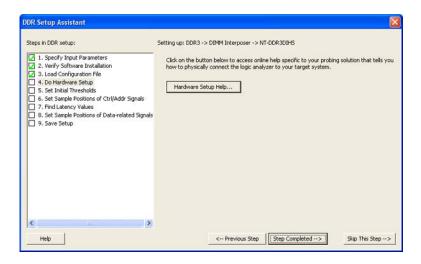

## **Step - Do Hardware Setup**

The DDR Setup Assistant takes no actions in this step; it just waits until you tell it the step is completed.

In this step, you must make the proper connections between the device under test and the logic analyzer. This includes:

- Connecting the probing solution to the device under test. (For more information, see Chapter 1, "Options for Probing DDR Devices," starting on page 11.)

- Connecting the probing solution to the logic analyzer.

When connecting the probing solution to the logic analyzer, the configuration's probe set maps out the probing solution to logic analyzer connection. To access the probe set's mapping:

- **1** Go to the *Agilent Logic Analyzer* application.

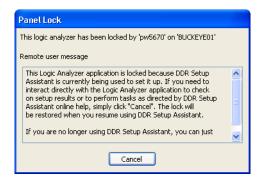

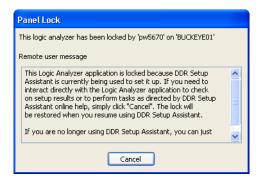

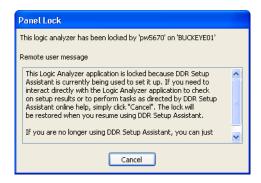

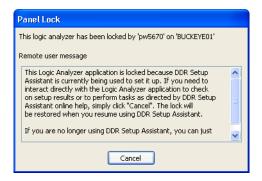

- 2 You may have to click Cancel in the Panel Lock dialog.

**3** In the *Agilent Logic Analyzer* application, click the **Overview** tab (or the System Overview icon) to view the Overview window.

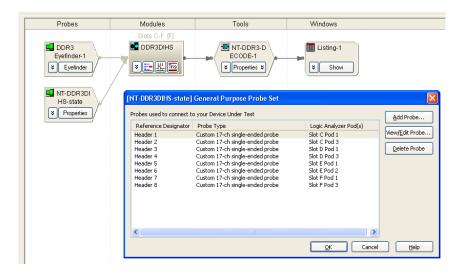

In the Overview window, you see a picture of the Probes, Modules, Tools, and Windows used in the configuration.

4 Click the probe's **Properties** button.

The General Purpose Probe Set dialog shows how the probe's reference designators map to the logic analyzer pod cables. For example:

NOTE

The General Purpose Probe Set mapping is different for each configuration. Yours will like be different than the one shown in the previous screen.

**5** Carefully connect the probes to the logic analyzer pod cables using the mapping shown in the General Purpose Probe Set dialog.

After you have made the proper probing solution to device under test and probing solution to logic analyzer connections, click **Step Completed** -->.

Next • "Step - Set Initial Thresholds" on page 42

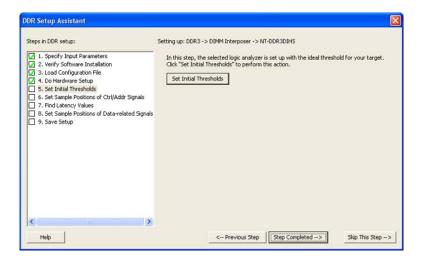

## **Step - Set Initial Thresholds**

In the **Set Initial Thresholds** step, the DDR Setup Assistant automatically sets the initial threshold voltages and detects if there are any problems with the settings.

- 1 Set up your device under test to have read and write traffic (see "Setting Up Read and Write Traffic in the DUT" on page 31).

- 2 Click Set Initial Thresholds.

The DDR Setup Assistant analyzes the swing of certain control signals to determine the best threshold voltage settings.

- **3** If there are problems with the automated initial threshold voltage settings, use the default threshold specified by the configuration file.

- 4 Click Step Completed -->.

Next

• "Step - Set Sample Positions of Ctrl/Addr Signals (not applicable to U4154A Logic Analyzer)" on page 47

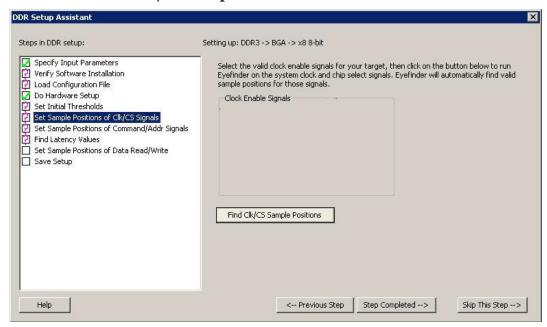

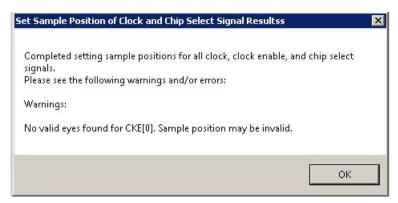

# Step - Set Sample Positions of Clk/CS Signals (only applicable to U4154A Logic Analyzer)

In this step, you set the sample positions of clock and chip select signals when using the U4154A Logic Analyzer module. For this step, DDR Setup Assistant runs the eyescan feature of the U4154A Logic Analyzer module to automatically calculate and set the optimal sample positions for the clock and chip select signals.

This step is only applicable to the U4154A Logic Analyzer.

NOTE

If you selected DDR4 as the bus type in step 1 - Specify Input Parameters, then an additional field **DDR4 Command Latency** is displayed in this step.

DDR4 Command latency is defined as the number of clocks from chip select going low until the command and address busses are valid.

Select valid clock enable signals and specify a value (ranging from 0 to 6) for DDR4 Command Latency.

**2** If the eyescan run completes but gives you warnings, you should check the warnings and re-run if necessary.

#### 3 Using the DDR Setup Assistant

**3** When the clock and chip select signal sample positions have been properly set, click **Step Completed** -->.

Next • "Step - Set Sample Positions of Command/Addr Signals (only applicable to U4154A Logic Analyzer)" on page 45

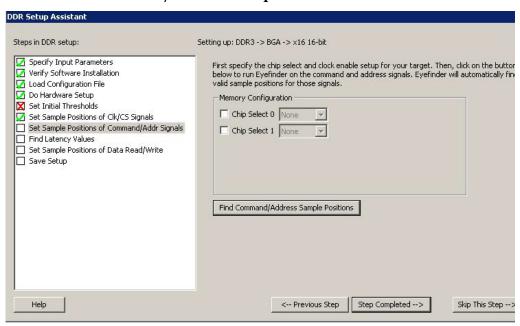

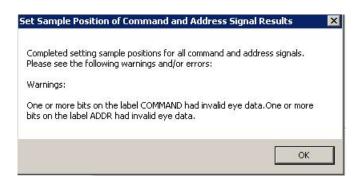

# Step - Set Sample Positions of Command/Addr Signals (only applicable to U4154A Logic Analyzer)

In this step, you set the sample positions of command and address signals when using the U4154A Logic Analyzer module. For this step, DDR Setup Assistant runs the eyescan feature of the U4154A Logic Analyzer module to automatically calculate and set the optimal sample positions for the command and address signals.

This step is only applicable to the U4154A Logic Analyzer.

1 Click Find Command/Address Sample Positions.

**2** If the eyescan run completes but gives you warnings, you should check the warnings and re-run if necessary.

#### 3 Using the DDR Setup Assistant

You should determine the cause of these messages by looking at the Agilent Logic Analyzer application's Thresholds and Sample Positions dialog and perhaps re-running the set up. See "Setting Up Thresholds and Sample Positions on DDR Address/Control Signals" on page 67.

**3** When the command and address signal sample positions have been properly set, click **Step Completed** -->.

Next • "Step - Find Latency Values" on page 49

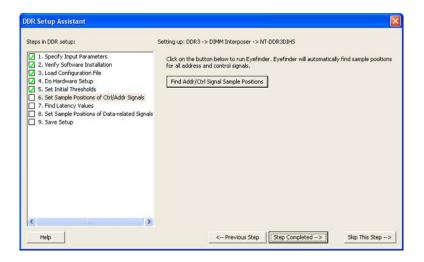

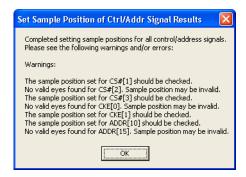

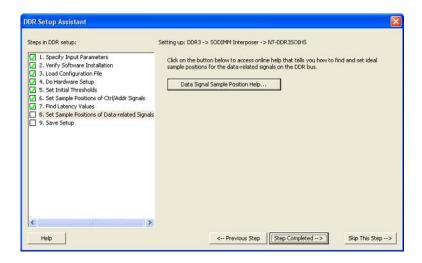

# Step - Set Sample Positions of Ctrl/Addr Signals (not applicable to U4154A Logic Analyzer)

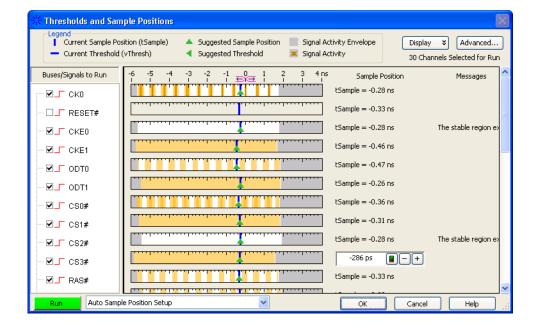

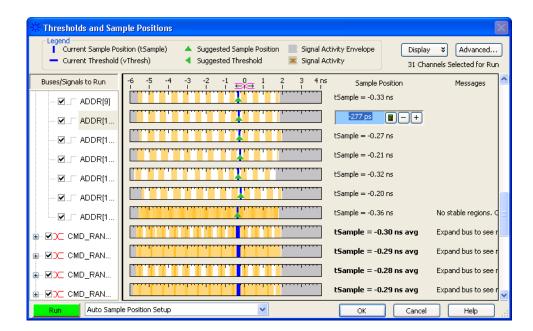

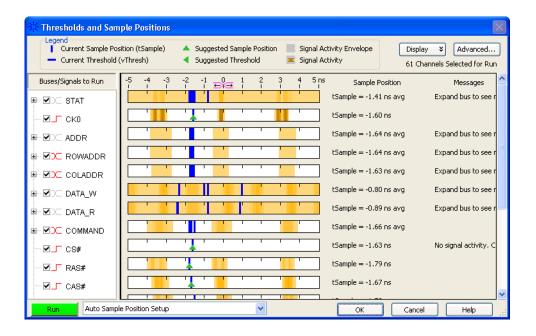

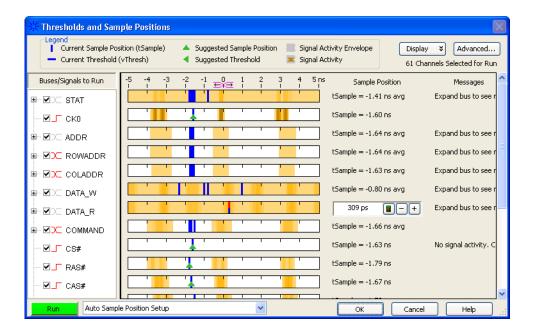

In this step, the DDR Setup Assistant runs the logic analyzer Thresholds and Sample Positions set up (also known as normal logic analyzer *eye finder*) to set the sample positions of the Control and Address signals.

This step is not applicable to the U4154A Logic Analyzer.

- 1 Again, make sure your device under test has read and write traffic (see "Setting Up Read and Write Traffic in the DUT" on page 31).

- 2 Click Find Addr/Ctrl Signal Sample Positions.

- **3** If the Thresholds and Sample Positions set up cannot run for some reason, click **Addr/Ctrl Signal Sample Position Help...** (which directs you to "If there are problems with finding Ctrl/Addr sample positions" on page 48).

- 4 If the Thresholds and Sample Positions set up run completes but gives you warnings, you should check the warnings and re-run if necessary.

For example, in the previous dialog, it may be that the CS#1-3, CKE0-1, ADDR15 signals are not being used, and these messages can safely be ignored. However, ADDR10 is generally used, so you should determine the cause of these messages by looking at the *Agilent Logic Analyzer* application's Thresholds and Sample Positions dialog and perhaps re-running the set up. See Chapter 4, "Setting Up Thresholds and Sample Positions on DDR Address/Control Signals," starting on page 67.

**5** When the Addr/Ctrl signal sample positions have been properly set, click **Step Completed -->**.

Next • "Step - Find Latency Values" on page 49

#### If there are problems with finding Ctrl/Addr sample positions

Generally, problems finding the Ctrl/Addr signal sample positions are basic. Check these things:

- Make sure the device under test is powered on and that the probing solution connections to the device under test and to the logic analyzer are good.

- Make sure there is memory traffic on the DDR bus. Dense traffic is better than sparse traffic when running the logic analyzer Thresholds and Sample Positions set up to determine the Ctrl/Addr signal sample positions.

See Also • "Solving Problems with Thresholds and Sample Positions Set Up" on page 72

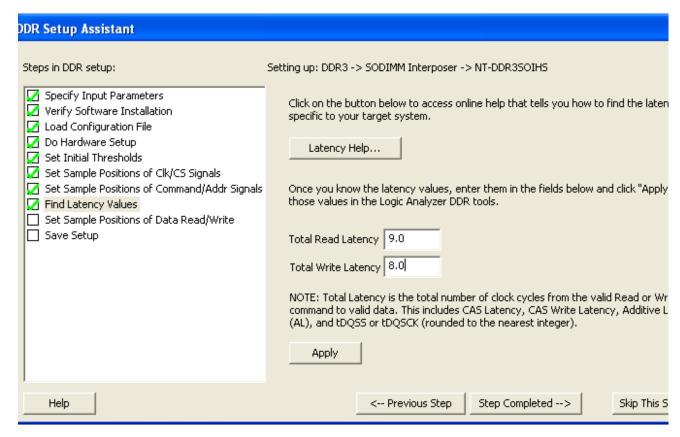

## **Step - Find Latency Values**

In this step, if you don't already know the latency values of the device under test, you set up the Mode Register Settings (MRS) trigger, take a trace, and scan it for latency values. See:

• "Taking a Mode Register Settings (MRS) Trace" on page 50

When you have the proper latency values for the device under test, enter the values into the DDR Setup Assistant; then, click **Apply**.

NOTE

The latency values that you specify in this step represent the total latency for your system and therefore should include parameters that affect total latency. For instance, if your system has Additive Latency (AL), then you must include it in the Total Latency values. Similarly, if tDQSS or tDQSCK parameters are greater than one full clock cycle, then you must add these values (rounded to the nearest integer) in the Total Latency values.

When you apply the latency values settings, the DDR Setup Assistant automatically transfers these settings to the DDR Bus Decoder and in the DDR3 Eyefinder / Eyescan.

You can also modify the DDR Bus Decoder and DDR3 Eyefinder / Eyescan settings yourself (or edit them later) by following these instructions:

- "Setting Latency Values in DDR Bus Decoder" on page 53

- "Setting Latency Values in DDR3 Eyefinder" on page 55

- "Setting Latency Values in Eyescan" on page 56

When you have found and transferred the latency values, click **Step Completed** -->.

#### Next

- "Step Set Sample Positions of Data-related Signals (not applicable to U4154A logic analyzer)" on page 60

- "Step Set Sample Positions of Data Read/Write (only applicable to U4154A Logic Analyzer)" on page 61

#### Taking a Mode Register Settings (MRS) Trace

- 1 Go to the Agilent Logic and Protocol Analyzer application.

- 2 You may have to click Cancel in the Panel Lock dialog.

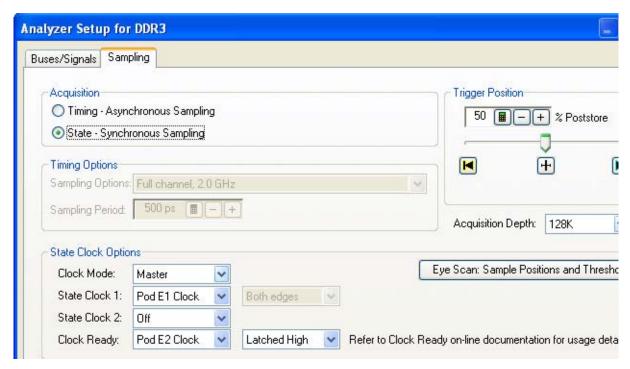

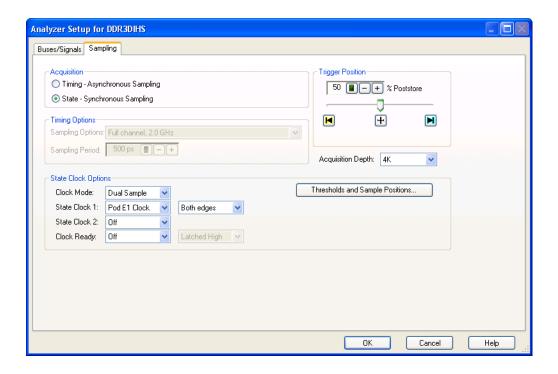

**3 For 16962A or 16960A Logic Analyzers** - In the Agilent and Protocol Logic Analyzer application's Sampling Setup, change the **Clock Ready** state clock option to **Latched High** for the clock input of Pod 2 (Clk2) as displayed in the following screen.

The CKE0 signal is routed to the CLK input on pod 2 of the logic analyzer module and CK0 is routed to the CLK input on pod 1.

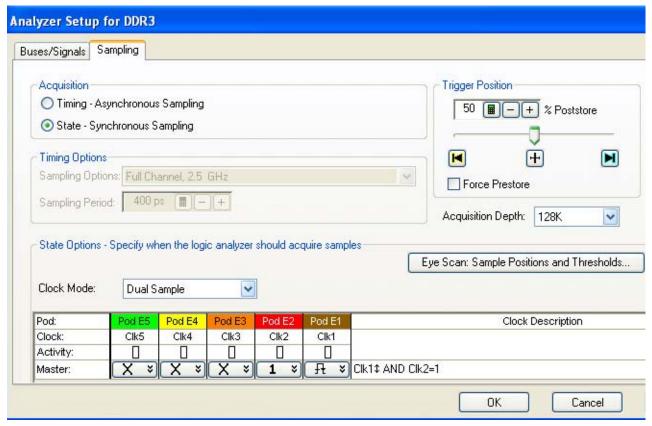

**For U4154A Logic Analyzers** - In the Agilent Logic and Protocol Analyzer application's Sampling Setup, set the clock input of Pod 2 (Clk2) as the state clock qualifier - **Qualifier** - **High** as displayed in the following screen. Notice that the Qualifier - High option is represented by "1" in the following screen.

- 4 Power off the device under test.

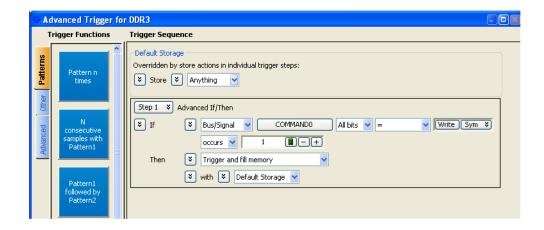

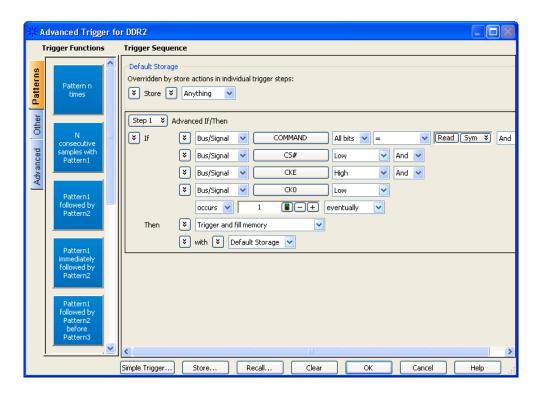

- 5 In the *Agilent Logic Analyzer* application's Advanced Trigger dialog, recall the **Mode Register Settings** trigger.

#### NOTE

If your device under test does not complete Mode Register Setting before the first memory write, change the Mode Register Settings trigger by replacing the sequence step that triggers on the first memory write with the "Run until user stop" trigger function. (Do not change the default storage.)

**6** Run the logic analyzer with Mode Register Settings trigger (clock ready latched high on CKE0\_qual)

The logic analyzer runs status shows "Waiting for trigger in Trigger Step 1...".

- 7 Power on the device under test.

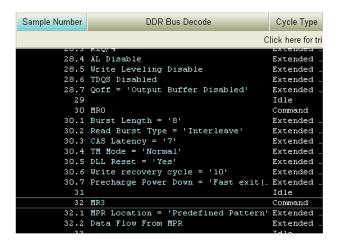

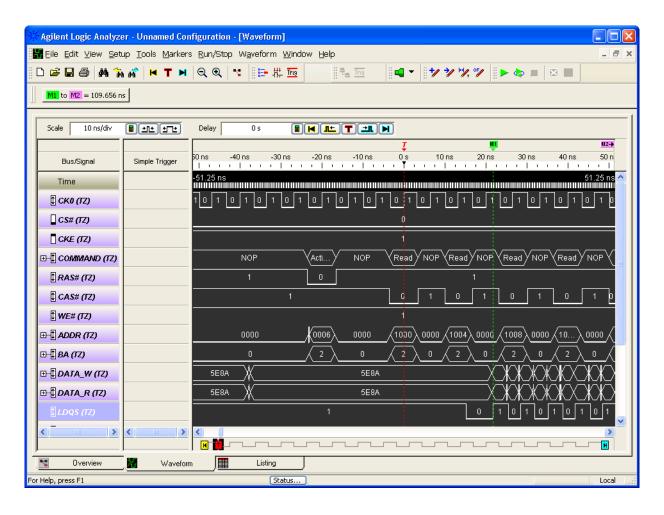

- **8** In the *Agilent Logic Analyzer* application's Listing window, go to the trigger.

The trigger is the first Write to Memory.

**9** Scroll backward from the trigger to find the last Latency settings before the memory write.

- **10** Record the values for:

- Read latency.

- Write latency.

- Burst length.

- Burst type (sequential or interleaved).

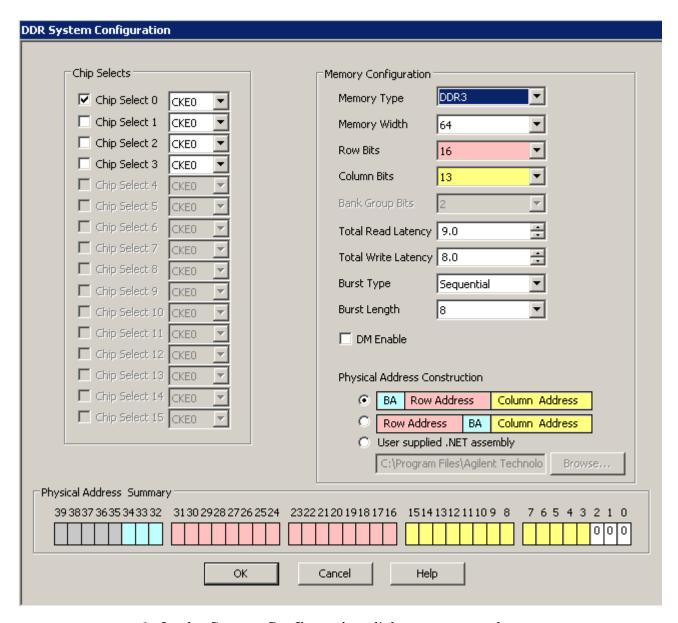

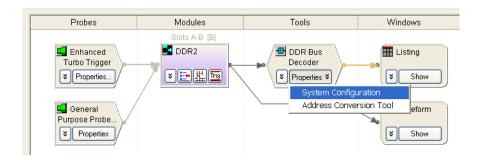

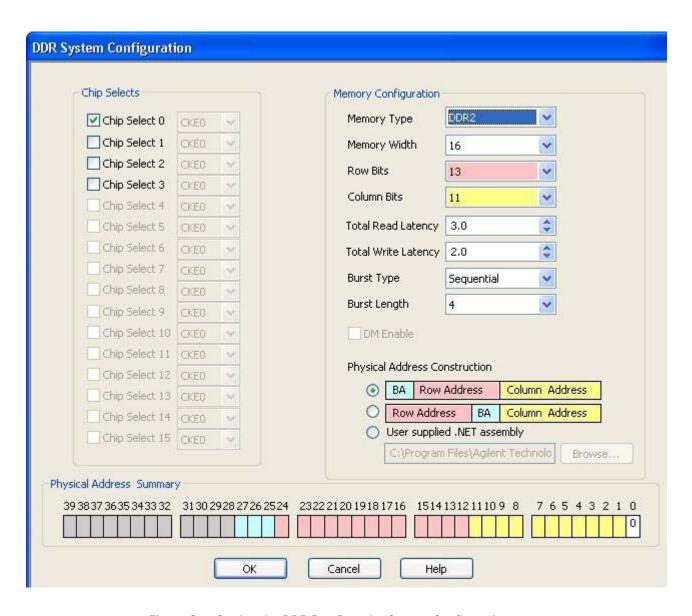

## **Setting Latency Values in DDR Bus Decoder**

To set the device under test's latency and burst values in the DDR Bus Decoder:

- 1 In the *Agilent Logic and Protocol Analyzer* application, click the **Overview** tab (or the System Overview icon) to view the Overview window.

- 2 In the DDR Bus Decoder tool (in the Tools column), click the **Properties** button and choose **System Configuration**.

The **System Configuration** dialog is displayed.

- 3 In the **System Configuration** dialog, enter or select:

- The appropriate Chip Select and CKE for the device under test.

- **Total Read Latency**(or **Read Offset**in some decoders) Enter the total Read latency value recorded earlier.

- Total Write Latency(or Write Offsetin some decoders) Enter the total Write latency value recorded earlier.

NOTE

The latency values that you specify in the System Configuration dialog represent the total latency for your system and therefore should include parameters that affect total latency. For instance, if your system has Additive Latency (AL), then you must include it in the Total Latency values. Similarly, if tDQSS or tDQSCK parameters are greater than one full clock cycle, then you must add these values (rounded to the nearest integer) in the Total Latency values.

- Burst Type— Enter the Burst type value recorded earlier.

- Burst Length— Enter the Burst length value recorded earlier.

- 4 Click OK.

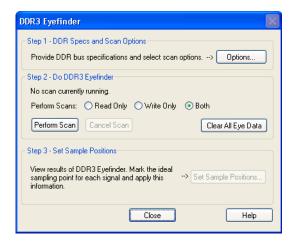

#### **Setting Latency Values in DDR3 Eyefinder**

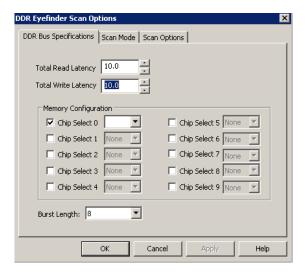

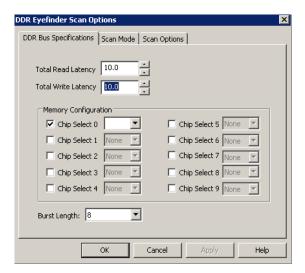

To set the device under test's latency and burst values in DDR3 Eyefinder:

- 1 In the *Agilent Logic and Protocol Analyzer* application, click the **Overview** tab (or the System Overview icon) to view the Overview window.

- 2 In the DDR3 Eyefinder probe (in the column on the left), click the **Eyefinder** button.

- 3 In the DDR3 Eyefinder dialog, click Options....

**4** In the DDR3 Eyefinder Scan Options dialog's DDR Bus Specifications tab, enter or select:

- Total Read Latency— Enter the total read latency value recorded earlier.

- Total Write Latency— Enter the total Write latency value recorded earlier.

NOTE

The latency values that you specify in the DDR3 Eyefinder represent the total latency for your system and therefore should include parameters that affect total latency. For instance, if your system has Additive Latency (AL), then you must include it in the Total Latency values. Similarly, if tDQSS or tDQSCK parameters are greater than one full clock cycle, then you must add these values (rounded to the nearest integer) in the Total Latency values.

- **Memory Configuration** Choose the appropriate Chip Select(s) for the memory path being traced.

- Burst Length— Enter the Burst length value recorded earlier.

- 5 Click **OK**.

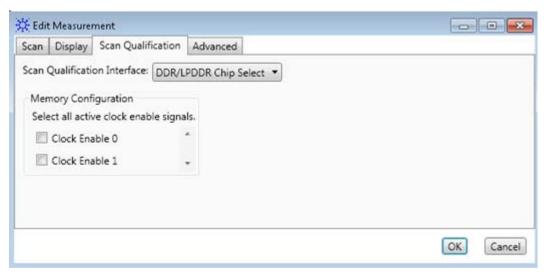

## **Setting Latency Values in Eyescan**

When using the U4154A Logic Analyzer module, you can modify the device under test's latency and burst values in Eyescan. The Eyescan feature of U4154A displays the default latency values or the latency values that you initially set using the DDR Setup Assistant tool. If required, you can modify these values for subsequent eyescan runs.

To modify the latency and burst values using the Eyescan feature:

- 1 In the Agilent Logic and Protocol Analyzer application, click the Overview tab (or the System Overview icon) to view the Overview window.

- 2 Click the Sampling Setup icon in the U4154A logical module displayed under the Modules column in the Overview window.

The Sampling tab of the Analyzer Setup dialog box is displayed.

- 3 Click the Eye Scan: Sample Positions and Thresholds... button.

- The Eye Scan Sample Position and Threshold Settings dialog box is displayed.

- 4 In the Eye Scan Sample Position and Threshold Settings dialog box, select the tab for Chip Select, Command and Address, Data Read or Data Write to modify the scan qualification for the appropriate signals.

5 Click the Edit Current Measurement 📝 toolbar button.

The Edit Measurement dialog box is displayed.

- 6 Click the Scan Qualification tab in this dialog box.

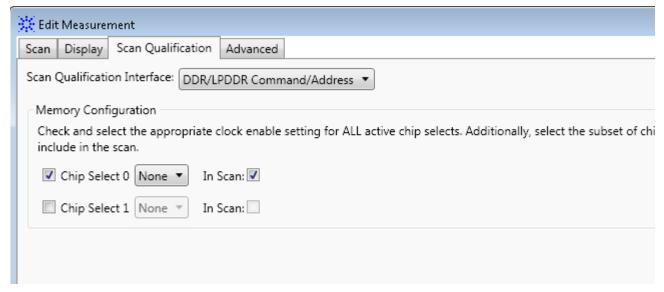

- **7** Based on the signals tab you selected in step 4, the options are displayed in the Scan qualification interface listbox. Select one of the following options from this listbox:

- DDR/LPDDR Chip Select option to modify the scan qualification for chip select signals.

- DDR/LPDDR Command and Address option to modify the scan qualification for command and address signals.

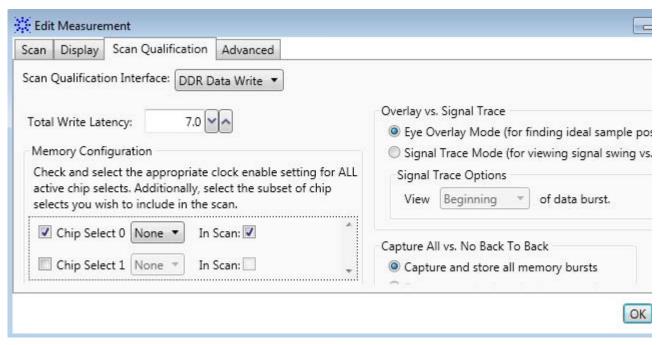

- DDR Data Read option to modify the scan qualification for data read signals.

- DDR Data Write option to modify the scan qualification for data write signals.

On selecting the DDR/LPDDR Chip Select option in the previous step, the following fields are displayed for chip select scan qualification:

#### **3** Using the DDR Setup Assistant

**8** For the DDR/LPDDR Chip Select signals, make the appropriate selections based on the active clock enable signals.

On selecting the DDR/LPDDR Command and Address option in the step 7, the following fields are displayed for scan qualification:

**9** For the DDR/LPDDR Command and Address signals, make the appropriate Memory Configuration selections based on the chip selects used in the DUT.

On selecting the **DDR/LPDDR Data Read** or **Data Write** interface in step 7, the following fields are displayed for scan qualification:

#### 10 For DDR Data Read or Write signals:

**g** The DUT's Total Read/Write Latency value that you set up in the initial DDR setup is displayed. If needed, modify this value. To find an appropriate value of Total Read/Write Latency, you can set up the Mode Register Settings (MRS) trigger, take a trace, and scan it for latency values.

NOTE

The latency values specified here represent the total latency for your system and therefore should include parameters that affect total latency. For instance, if your system has Additive Latency (AL), then you must include it in the Total Latency values. Similarly, if tDQSS or tDQSCK parameters are greater than one full clock cycle, then you must add these values (rounded to the nearest integer) in the Total Latency values.

- **h** In the **Memory Configuration** section, choose the appropriate Chip Select(s) for the memory path being traced.

- i In the **Burst Length** field, specify the number of words read or written for each read/write command. To find appropriate value of Burst Length for the DUT, you can set up the Mode Register Settings (MRS) trigger, take a trace, and scan it for burst length.

- 11 Click **OK** to confirm the settings.

You can save the modified latency and burst values in the Logic Analyzer .ala or .xml configuration file.

# Step - Set Sample Positions of Data-related Signals (not applicable to U4154A logic analyzer)

In this step, you set the sample positions of Data signals.

- With the 16960A or 16962A logic analyzers, use DDR3 Eyefinder to set the sample positions of data signals. See "Your First DDR3 Eyefinder Scan (16962A logic analyzers only)" on page 76.

- With the 16950A/B or 16951B logic analyzers, use the logic analyzer's *timing zoom* feature to set the sample positions of data signals. See Appendix A, "Setting Data Sample Positions with the 1695x Logic Analyzers," starting on page 115.

This step is not applicable to U4154A Logic Analyzer module. For setting the sample positions of Data signals when using the U4154A module, refer to the topic "Step - Set Sample Positions of Data Read/Write (only applicable to U4154A Logic Analyzer)" on page 61.

After setting the sample positions of Data signals, click Step Completed -->.

Next • "Step - Save Setup" on page 65

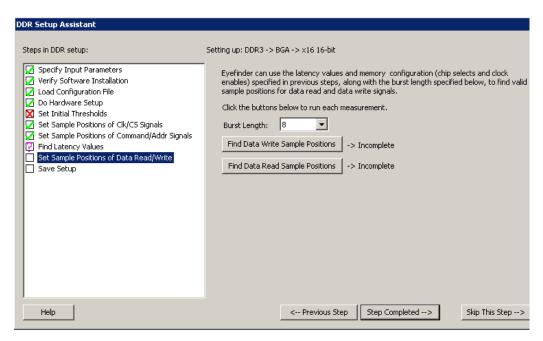

# Step - Set Sample Positions of Data Read/Write (only applicable to U4154A Logic Analyzer)

In this step, you set the sample positions of Data signals when using the U4154A Logic Analyzer module.

NOTE

The fields displayed in this step differ if you selected DDR4 bus type in step 1. Therefore, the procedure for setting sample positions for DDR4 Data signals is described separately in this topic.

For this step, DDR Setup Assistant runs the eyescan feature of the U4154A Logic Analyzer module to automatically calculate and set the optimal sample positions for the data signals.

- Click **Find Data Write Sample Positions** to find the optimal and valid sample positions for the data write signals.

- Click **Find Data Read Sample Positions** to find the optimal and valid sample positions for the data read signals.

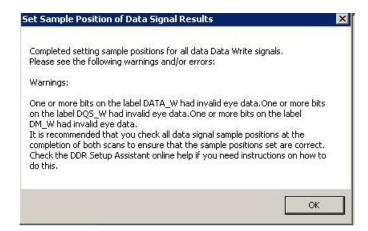

If the eyescan run completes but gives you warnings, you should check the warnings and re-run the eyescan in this step.

After setting the sample positions of Data signals, click Step Completed -->.

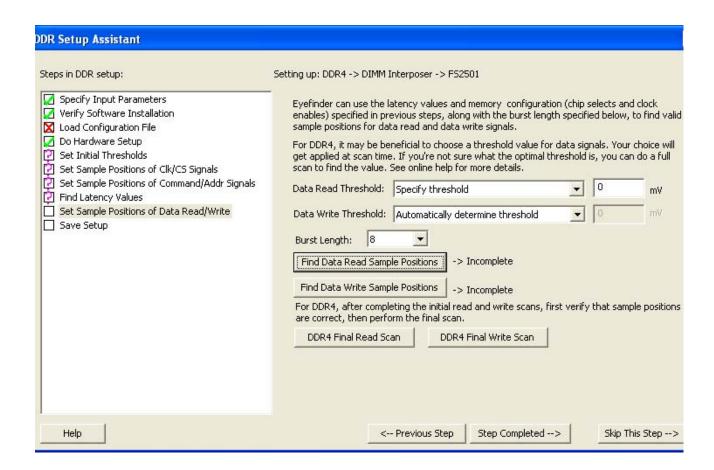

#### To find and set sample positions for DDR4 Data related signals

- 1 Set the threshold for DDR4 data read and write signals. You can set the threshold in either of the following two ways:

- From the **Data Read Threshold** and **Data Write Threshold** listboxes, select the **Automatically determine threshold** option to let DDR Setup Assistant automatically determine the best threshold setting. The middle of the signal swing is used in this case.

- From the **Data Read Threshold** and **Data Write Threshold** listboxes, select the **Specify threshold** option to manually specify the threshold value. This is particularly useful in case of DDR4 signals for which the automatically determined threshold value may not be an ideal threshold to use.

If you selected to manually specify the threshold value for DDR4 data signals, you can determine the best threshold setting by performing the following steps:

- i Access the already open Logic and Protocol Analyzer application. To do this, you need to cancel the "Panel Lock" dialog displayed by DDR Setup Assistant.

- ii Open the **Setup** dialog box of the logic analyzer module.

- iii Click the Sampling tab.

- iv Click the Eye Scan: Sample Positions and Thresholds button

- v Click the Data Read measurement tab.

- vi Click Edit Current Measurement toolbar button and then select Do full time/voltage scan in the Scan tab.

- vii Click OK.

- viii Run the eyescan measurement by clicking Run this measurement.

- ix View the eyescan results to decide which threshold is likely to result in the best eye openings. Note down the threshold value. If required, you can unlock the threshold settings to move the threshold marker.

- x Click the **Data Write** measurement tab.

- xi Repeat steps vi-ix to view threshold for the Data Write measurement.

- xii Once you have noted down the threshold that would result in best eye openings, click Cancel to cancel the Eye scan Sample Positions and Threshold Settings dialog.

- xiii Click Cancel again to cancel the Analyzer Setup dialog.

- xiv Access the already open DDR Setup Assistant and specify the obtained threshold values in the **Data Read Threshold** and **Data Write Threshold** fields.

- 2 Select the Burst Length.

- **3** Click **Find Data Read Sample Positions** to find the optimal and valid sample positions for the data read signals based on the specified threshold settings.

- 4 Click **Find Data Write Sample Positions** to find the optimal and valid sample positions for the data write signals based on the specified threshold settings.

- 5 Once you have verified that the obtained sample positions for DDR4 data read and write signals are correct, perform a final scan. You perform a final scan by clicking the **DDR4 Final Read Scan** and **DDR4 Final Write Scan** buttons.

A final scan is a comparatively shorter scan than a main scan and is used to perform a final setting to fine tune the obtained sample positions. A final scan verifies that the sample positions are optimal not just for the first bit but for all 8 bits in the burst.

Based on the fine tuning needed, a final scan may result in only a minor change or no change at all to the sample positions.

Next "Step - Save Setup" on page 65

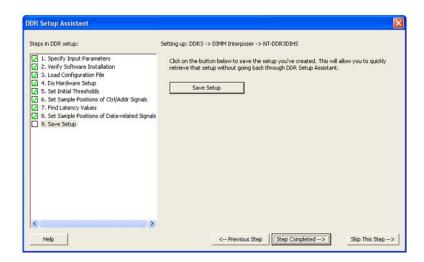

# **Step - Save Setup**

In this step, save your logic analyzer setup so that it can be opened later without having to perform the DDR Setup Assistant steps again..

1 Click Save Setup.

- 2 In the Save Setup dialog, browse to the location where you want to save the setup file, enter the file name, and click **Save**.

- 3 In the message dialog that says the setup was saved successfully, click **OK**.

- 4 Click **OK**.

After saving the configuration, click **Step Completed -->**.

Next • "Setup Complete" on page 66

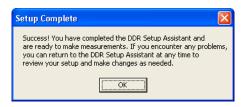

# **Setup Complete**

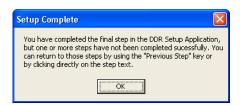

After clicking **Step Completed -->** in the last step of the DDR Setup Assistant, you get a Setup Complete message.

The Setup Complete mesasge will tell you if any of the steps still need to be completed.

When the DDR setup is complete, you can use the DDR bus decoder and other tools to analyze captured data.

#### See Also

- Chapter 4, "Setting Up Thresholds and Sample Positions on DDR Address/Control Signals," starting on page 67

- Chapter 5, "Using DDR3 Eyefinder," starting on page 75

- Chapter 7, "Validating the DDR Setup," starting on page 107

- Chapter 8, "Capturing Data (Triggering)," starting on page 109

- Chapter 9, "Decoding Captured Data," starting on page 113

# Setting Up Thresholds and Sample Positions on DDR Address/Control Signals

Setting Up Thresholds and Sample Positions 68

Solving Problems with Thresholds and Sample Positions Set Up 72

The Thresholds and Sample Positions dialog in the *Agilent Logic Analyzer* application's sampling setup tab (also known as normal logic analyzer *eye finder*), is used to set the sampling positions of the DDR address and control signals. This is necessary before DDR3 Eyefinder can be used to set the data signal sample positions on 16960A or 16962A logic analyzers.

For U4154A logic analyzer, the DDR Setup Assistant sets the sampling positions on DDR command, address, and data read and write signals using the U4154A eyescan feature. This feature is also available in the Agilent Logic Analyzer application. You can also set the threshold and sample positions on individual channels of U4154A using the Eye Scan - Sample positions and Threshold Settings dialog box accessible by clicking the Eye scan: Sample Positions and threshold button in the Sampling tab of the Setup dialog box.

The DDR Setup Assistant runs the Thresholds and Sample Positions set up for you; however, it may run into some problems that require you to open and re-run the set up.

## **Setting Up Thresholds and Sample Positions**

The Thresholds and Sample Positions set up (also known as normal logic analyzer *eye finder*) is used to set the sampling positions of the DDR address and control signals. This is necessary before DDR3 Eyefinder can be used to set the data signal sample positions (on 16962A and 16960A logic analyzers).

- 1 Go to the Agilent Logic Analyzer application.

- 2 If you are currently using the DDR Setup Assistant, you may have to click **Cancel** in the Panel Lock dialog.

3 In the Agilent Logic Analyzer application, click the 🖺 Sampling Setup icon.

4 In the Sampling Setup dialog, click Thresholds and Sample Positions....

- 5 In the Thresholds and Sample Positions dialog, make sure the address and control signal sample positions are aligned.

- 6 If necessary, click Run to rerun the Thresholds and Sample Positions set up.

The resulting sampling positions should be aligned and just left of zero (0).

4 Setting Up Thresholds and Sample Positions on DDR Address/Control Signals

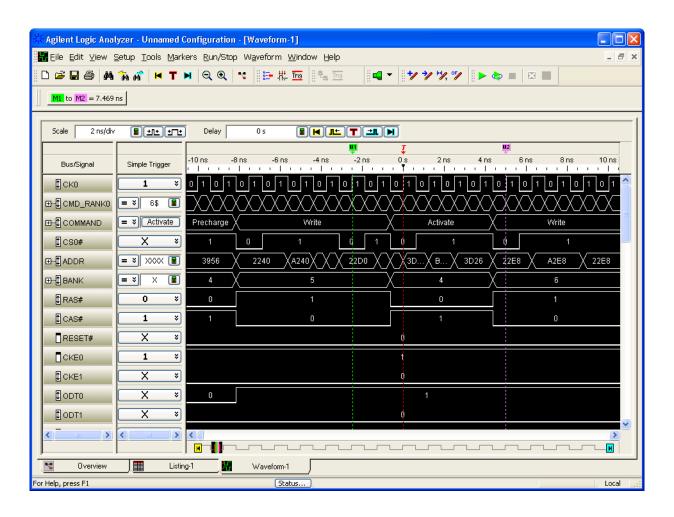

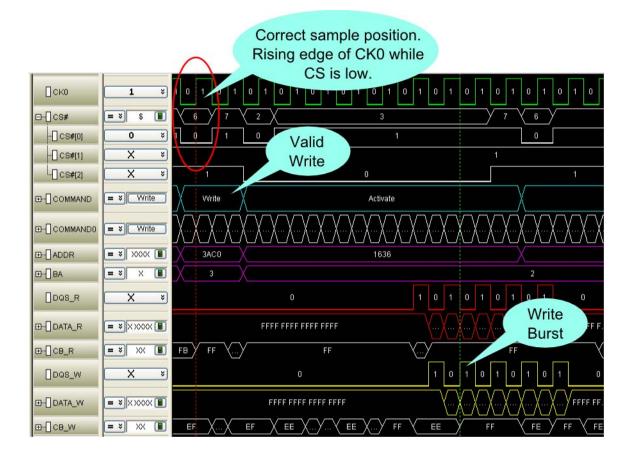

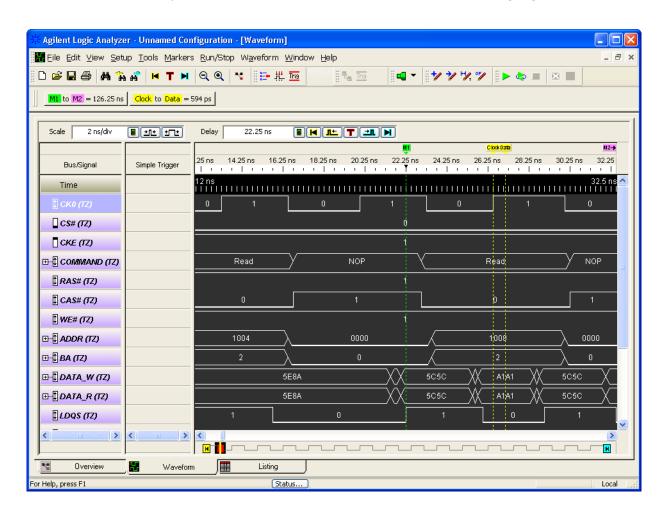

7 Take a trace to ensure that Command, CK, BANK, and ADDR are sampled correctly.

Because we are sampling on both the rising and falling edges of CK, you want to check that the rising edge of CK must be in the middle of CS# low.

# **Solving Problems with Thresholds and Sample Positions Set Up**

- "No eye finder or eye scan eyes for Address and Command" on page 72

- "Clock edges "too close together" error message on Run" on page 72

#### No eye finder or eye scan eyes for Address and Command

| Possible Cause:                                                                                                        | Possible Solution:                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The DDR device under<br>test's power saving<br>mode allows Address<br>and Control signals to<br>float when CKE is low. | <ul> <li>Try these steps:</li> <li>1 To verify the issue:</li> <li>a In Timing mode, trigger on CKE = low.</li> <li>b Check if the Address and Command signals appear to be tri-stated while CKE=low, that is, there are rapid changes in signals during CKE=low relative to activity during CKE=high.</li> <li>2 Disable Power saving mode in target BIOS until sample positions are set.</li> <li>3 Or Clock Ready set to Enable High.</li> </ul> |

| With 2T signaling,<br>Address is only valid<br>while CS# is low.                                                       | Set Sample positions for Address/Ctrl to same position as CS#.                                                                                                                                                                                                                                                                                                                                                                                      |

# Clock edges "too close together" error message on Run

Possible causes and solutions:

| Possible Cause:                        | Possible Solution:                                                                                                                                                                   |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Poor signal integrity on clock signal. | Check the clock signal quality by sampling the signal in timing mode, by using the logic analyzer Thresholds and Sample Positions set up in state mode, or by using an oscilloscope. |

| Possible Cause:                                | Possible Solution:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| You are attempting to take a trace from reset. | In the sampling setup, set Clock Ready to latch high on CKEO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Power management (clocks tri-state).           | <ul> <li>Try these steps:</li> <li>1 To verify the issue, in timing mode, Trigger on both CKE = low. Check if the clock appears to stop or tri-state when both CKEs are low.</li> <li>2 Change the CK0 threshold voltage setting from "differential" to 50 mV. This helps prevent the Clock edge error message as CK0 fluctuates at 0 V during tri-state.</li> <li>3 Or, disable Power Management mode in target BIOS.</li> <li>4 Or, use Clock Ready set to Enable High. (For older interposers, this works for single rank DIMMs if used on Dual Rank DIMMs. Some data from CKE1 rank could be lost when CKE0 is low when CKE1 isn't low. Newer FuturePlus interposers OR the CKE0 and CKE1 signals which is good for Dual and Quad Rank DIMMs.)</li> <li>5 Or, consider using the 4 GHz (250 ps) half channel timing mode on Addr/Ctrl signals for power management debug. You can also use the 8 GHz (125 ps) quarter channel timing mode, where E5386A adapters are typically used to reduce the number of probes and connectors required.</li> </ul> |  |

#### What to Expect if Clocks Tri-State

When CKE and CKE1 are both low – system entering self refresh - clocks will turn off.

When the clock tri-states, the Waveform display will be different:

- Time tags will be wrong for approximately 40 cycles before and after the clock tri-states.

- However, sampled data is accurate.

- The DDR Bus Decoder decodes self refresh and power down modes.

- 4 Setting Up Thresholds and Sample Positions on DDR Address/Control Signals

- It is best to view the Listing display in this situation.

DDR Setup Assistant

Online Help

# Using DDR3 Eyefinder

Getting Started with DDR3 Eyefinder (for 16962A/16960A) 76

Setting Scan Options 87

Performing Scans 93

Setting Sample Positions 94

Viewing Signal Swing vs. Time 99

Solving DDR3 Eyefinder Problems 100

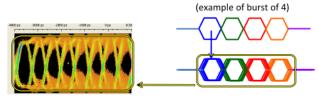

DDR3 Eyefinder is similar to the logic analyzer Thresholds and Sample Positions set up (also known as normal logic analyzer *eye finder*) except that it is specifically designed to find DDR3 data signal eyes, given the relationship between DDR3 control/address signals and data signals. DDR3 Eyefinder also provides additional features to help you locate data signal eyes and properly set sample positions, including the ability to analyze scan data using different scales, color schemes, and filtering.

#### NOTE

DDR3 Eyefinder can be used with the 16960A and 16962A logic analyzers. It cannot be used with the 16950A/B logic analyzers.

DDR3 Eyefinder is unable to perform threshold scans when used with the 16960A logic analyzer, and only time scans are available.

#### See Also

• Logic analyzer Thresholds and Sample Positions set up ("To automatically adjust state sampling positions and threshold voltages" (in the online help))

## Getting Started with DDR3 Eyefinder (for 16962A/16960A)

- "Before Running DDR3 Eyefinder" on page 76

- "Your First DDR3 Eyefinder Scan (16962A logic analyzers only)" on page 76

#### **Before Running DDR3 Eyefinder**

Before running DDR3 Eyefinder, you must set the sample positions for the control/address signals using the DDR Setup Assistant (see Chapter 3, "Using the DDR Setup Assistant," starting on page 33) or the logic analyzer Thresholds and Sample Positions set up (also known as normal logic analyzer *eyefinder*, see "To automatically adjust state sampling positions and threshold voltages" (in the online help)).

After setting the control/address signal sample positions, you can set up and run DDR3 Eyefinder scans.

#### Your First DDR3 Eyefinder Scan (16962A logic analyzers only)

We recommend your first DDR3 Eyefinder scan be a "threshold" scan to give you a good first picture of the signal eyes and proper sampling positions. This type of scan can take about an hour to complete, but the results are worthwhile.

- 1 Go to the Agilent Logic Analyzer application.

- 2 If you are using the DDR Setup Assistant, you may have to click **Cancel** in the Panel Lock dialog.

- **3** In the *Agilent Logic Analyzer* application, click the **Overview** tab (or the System Overview icon) to view the Overview window.

- **4** In the DDR3 Eyefinder probe (in the column on the left), click the **Eyefinder** button.

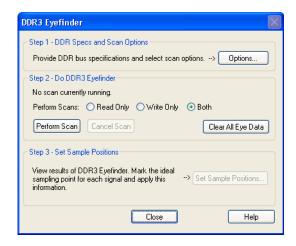

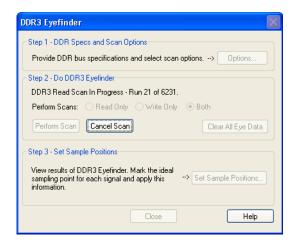

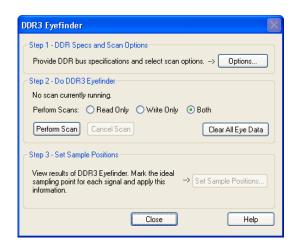

5 In the DDR3 Eyefinder dialog, first provide the scan values:

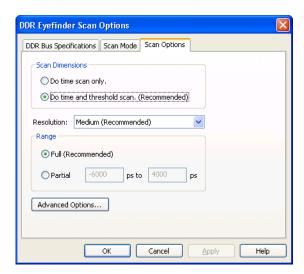

- a Click Options....

- b In the DDR Eyefinder Scan Options dialog's DDR Bus Specifications tab, enter the appropriate Total Read Latency, Total Write Latency, Memory Configuration, and Burst Length values.

If you do not know the appropriate values for your device under test, you can find the appropriate scan values using an Mode Register Settings (MRS) trigger as described in "Step - Find Latency Values" on page 49 and "Setting Latency Values in DDR3 Eyefinder" on page 55.

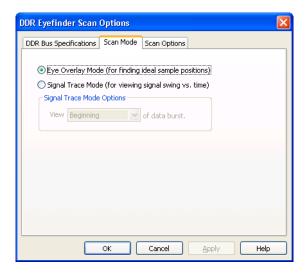

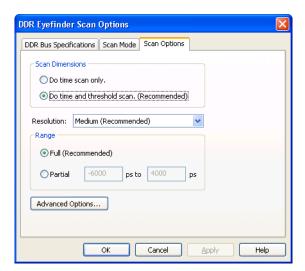

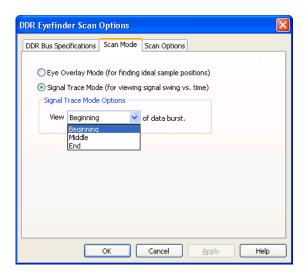

**c** In the **Scan Mode** tab, use the recommended settings (eye overlay mode).

**d** In the **Scan Options** tab, use the recommended settings (time and threshold scan, medium resolution, and full range).

e Click OK to save the scan values/options and close the dialog.

For more information on setting scan values and options, see "Setting Scan Options" on page 87.

6 Back in the DDR3 Eyefinder dialog, select **Both** read and write scans; then, click **Perform Scan** to run DDR3 Eyefinder scan.

As configured in the previous steps, the scan takes over an hour to complete. The DDR3 Eyefinder run status is shown in the dialog.

For more information on performing scans, see "Performing Scans" on page 93.

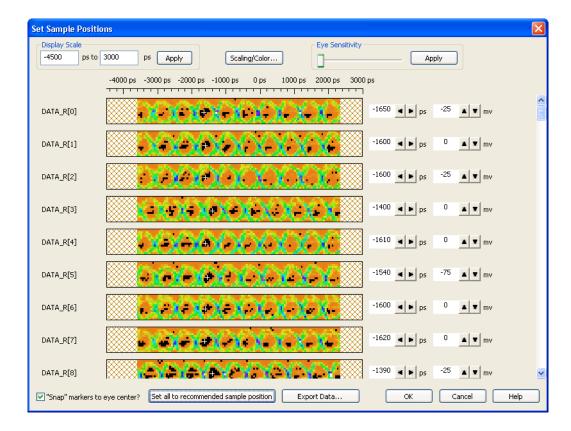

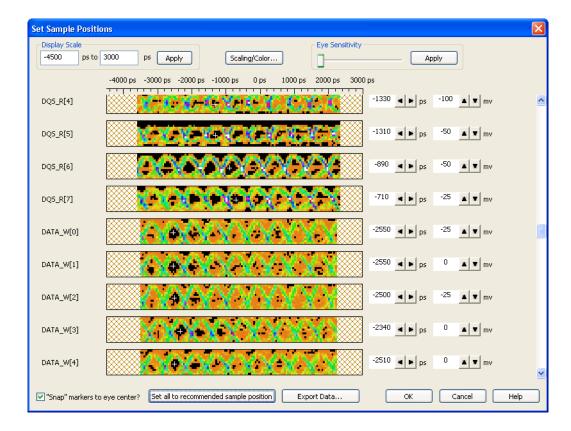

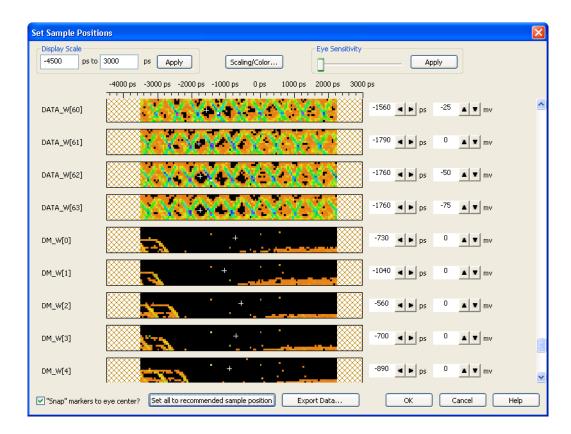

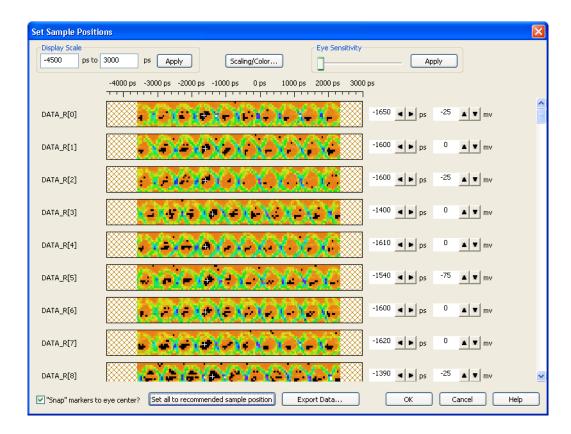

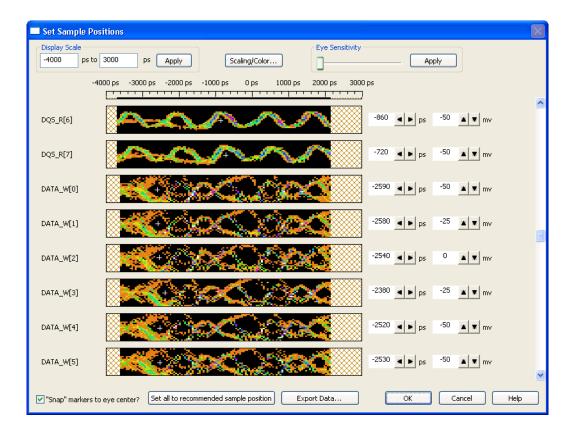

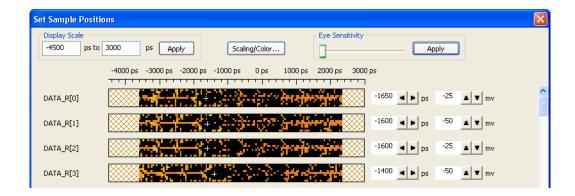

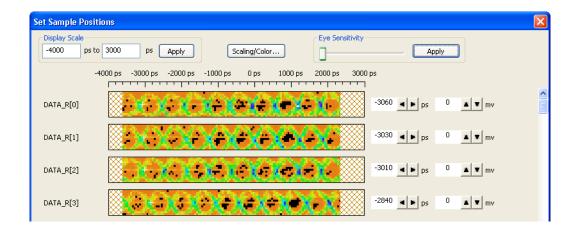

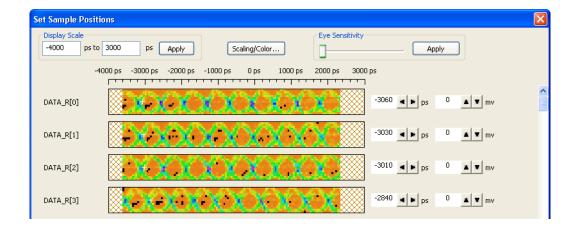

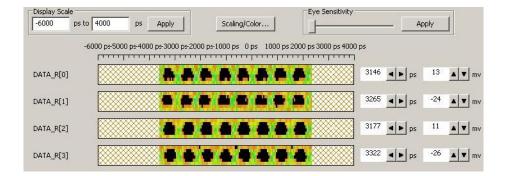

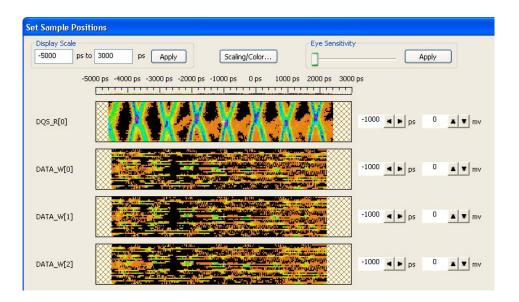

- 7 After the read and write scans complete, click **Set Sample Positions...** to view the scan results and set the sample positions.

- **8** In the Set Sample Positions dialog:

a Click Set all to recommended sample position.

The white crosshair markers show the recommended sample positions (see the following example).

CAUTION

Recommended sample positions might be at incomplete eyes nearest the last sample position settings. Always visually inspect the results of setting all to the recommended sample positions (see the next step).

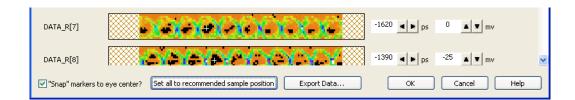

- **b** Scroll though the signals and adjust sample positions as necessary. You can uncheck the "Snap" markers to eye center? option for greater control over the sample position placement.

- Single-click to move to center of suggested eyes.

- When there is only one obvious eye, pick that eye.

- If there are problems, see "Solving DDR3 Eyefinder Problems" on page 100.

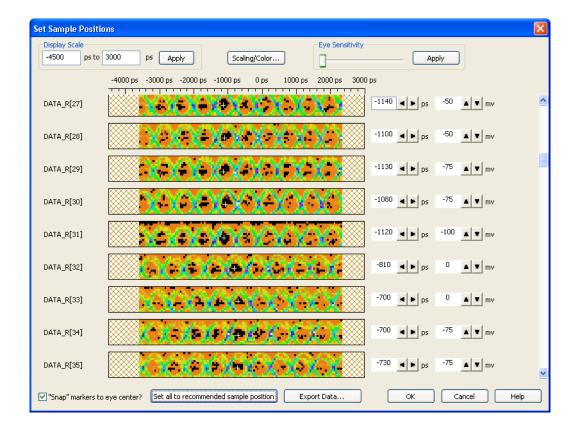

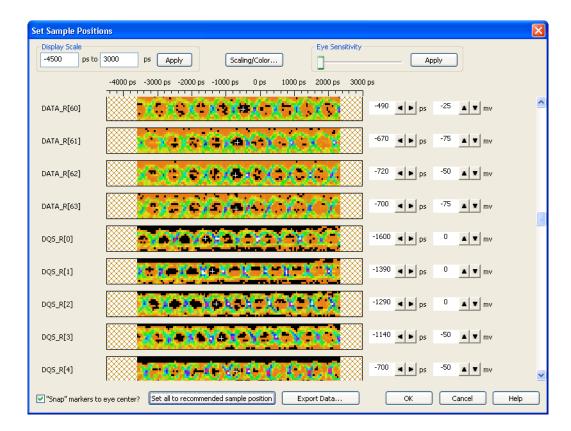

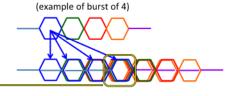

Take note of the eye positions for each group of eight signals. You may notice *byte shifts* on eight bit boundaries as shown in the following example.

It's important to note the eye positions for each byte lane (set of eight signals) because the strobe signal eyes are roughly at the same position as the corresponding byte lane. Knowing this can help you select the correct eyes for the strobe signals. The following example shows strobe eye position differences.

Data write signal eyes appear in different positions than data read signal eyes, as shown in the following example.

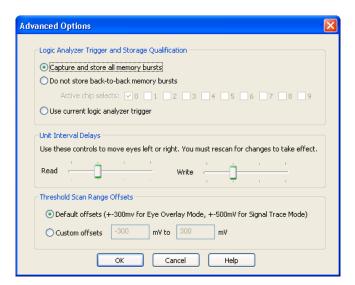

Sometimes for data read or write signals, two eyes appear. You can use the **Do not store back-to-back memory bursts** advanced scan option to prevent this (see "Setting Advanced Scan Options" on page 91). Higher resolution scans will also help clear up uncertainties.

You may notice signals that are not used, as in the following example.

**c** When you are done setting sample positions, click **OK**. Then, click **Yes** in the confirmation dialog.